【導(dǎo)讀】今天,大多數(shù)電源路線圖都將GaN晶體管作為一個(gè)關(guān)鍵平臺(tái)集成到其中�。與Si-mosfet、igbt和SiC-mosfet相比��,GaN晶體管的優(yōu)點(diǎn)意味著工程師們正在將它們廣泛地設(shè)計(jì)到他們的系統(tǒng)中�。然而,GaN晶體管在開關(guān)電源中的這些進(jìn)步也使得表征這些電源的性能變得越來越具有挑戰(zhàn)性��。在半橋上測(cè)量高邊VGS是診斷晶體管交叉導(dǎo)通的一種傳統(tǒng)方法�����,對(duì)于基于GaN的設(shè)計(jì)來說是一項(xiàng)艱巨的任務(wù)�。典型的解決方案是使用高成本的測(cè)量設(shè)備,這并不總是產(chǎn)生有用的結(jié)果��。本文介紹了一種利用GaN晶體管的獨(dú)特特性測(cè)量交叉導(dǎo)通的簡(jiǎn)單而經(jīng)濟(jì)的方法�����。

在升壓或降壓變換器和雙向變換器中用于同步整流的半橋和全橋配置為高����、低壓側(cè)晶體管使用互補(bǔ)驅(qū)動(dòng)信號(hào)�����。驅(qū)動(dòng)信號(hào)必須在半橋中的一個(gè)晶體管關(guān)閉和另一個(gè)晶體管打開之間包含少量的“死區(qū)時(shí)間”����,以確保晶體管不會(huì)交叉導(dǎo)電�����。當(dāng)半橋結(jié)構(gòu)中的晶體管同時(shí)打開時(shí)�����,會(huì)發(fā)生交叉?zhèn)鲗?dǎo)����,這種情況會(huì)增加損耗,并可能損壞晶體管�。增加死區(qū)時(shí)間有助于保護(hù)晶體管,但也會(huì)產(chǎn)生另一種類型的損耗�����,這種損耗會(huì)在兩個(gè)晶體管都關(guān)閉時(shí)發(fā)生,從而降低電橋的效率并降低功率轉(zhuǎn)換器的可用占空比范圍�。因此,在確保不發(fā)生交叉?zhèn)鲗?dǎo)的情況下���,盡量減少橋的停滯時(shí)間是一個(gè)關(guān)鍵的設(shè)計(jì)目標(biāo)。驗(yàn)證此操作是一個(gè)挑戰(zhàn)��。

驗(yàn)證電源半橋拓?fù)涫欠裾_交叉導(dǎo)通的常用方法是使用兩個(gè)探針同時(shí)驗(yàn)證高壓側(cè)和低壓側(cè)驅(qū)動(dòng)信號(hào)之間的死區(qū)時(shí)間�����。測(cè)量氮化鎵晶體管驅(qū)動(dòng)信號(hào)��,特別是高邊柵���,是一項(xiàng)具有挑戰(zhàn)性的工作����,經(jīng)常導(dǎo)致誤觸發(fā)�,使設(shè)計(jì)工程師感到沮喪。

GaN器件的柵極信號(hào)具有很高的轉(zhuǎn)換速率���,約為1V/ns�����,這給使用傳統(tǒng)的隔離探針進(jìn)行高邊測(cè)量帶來了挑戰(zhàn)�。如果測(cè)量系統(tǒng)沒有足夠的共模抑制比(CMRR),則高壓側(cè)源節(jié)點(diǎn)共模電壓的快速變化會(huì)產(chǎn)生干擾�����,使測(cè)量變得模糊��。另外����,傳統(tǒng)的無源電壓探針引入的寄生電容會(huì)使柵極驅(qū)動(dòng)信號(hào)失真,從而導(dǎo)致交叉?zhèn)鲗?dǎo)�����。

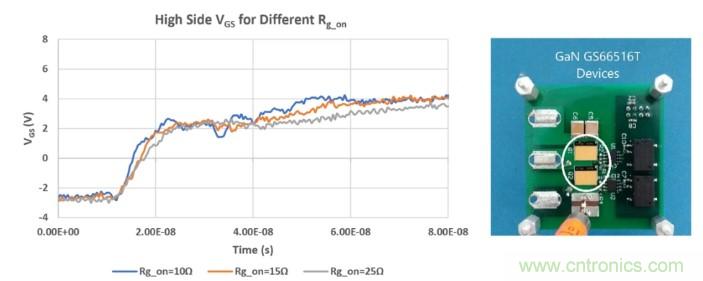

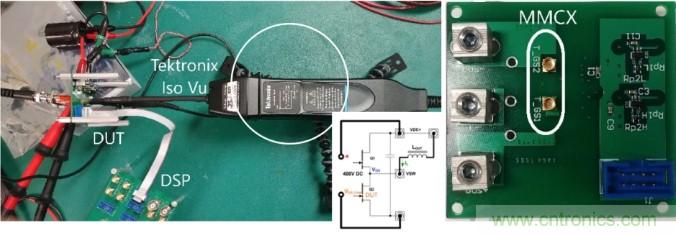

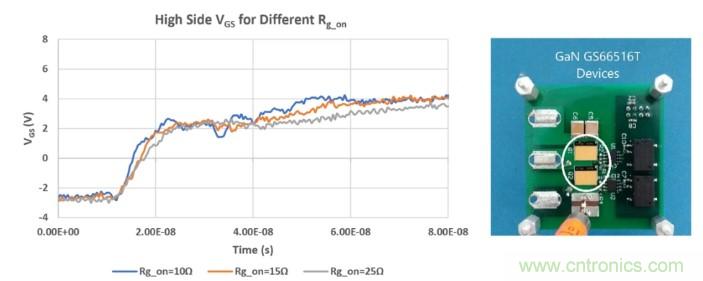

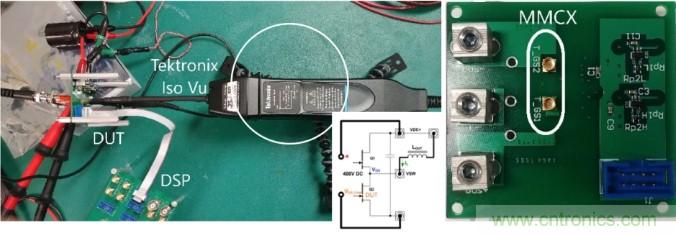

光學(xué)隔離測(cè)量系統(tǒng)�,如Tektronix TIVH系列IsoVu,已開發(fā)出直流共模抑制比大于160分貝�,以提供可實(shí)現(xiàn)的高壓側(cè)VGS測(cè)量解決方案。此類測(cè)量系統(tǒng)還必須最小化傳感回路面積����,并提供增強(qiáng)的屏蔽測(cè)量信號(hào)路徑�。為此�,配備了微型電容轉(zhuǎn)換器(cx)專用電路板,以提供所需功率的微型接口����。圖1顯示了使用GS66516T GAN晶體管的高側(cè)VGS測(cè)量結(jié)果和雙脈沖測(cè)試板。TIVH系列IsoVu和MMCX連接器用于實(shí)現(xiàn)這一點(diǎn)����,如圖2所示�。

圖1左邊的圖表顯示了使用Tektronix IsoVu測(cè)量系統(tǒng)在ILoad=23A下測(cè)量的不同Rgon的高壓側(cè)VG。右側(cè)顯示GS66516T雙脈沖測(cè)試(DPT)板�。

帶MMCX連接器的PCB板(右)。

測(cè)量系統(tǒng)的成本以及信號(hào)路徑的額外復(fù)雜性和靈敏度為更具成本效益和更不敏感的解決方案留下了空間����。GaN系統(tǒng)工程師開發(fā)的一種方法只測(cè)量低端晶體管,解決了這些問題���。

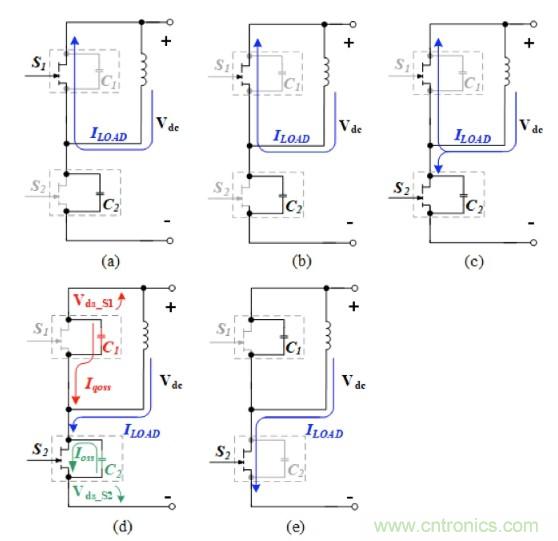

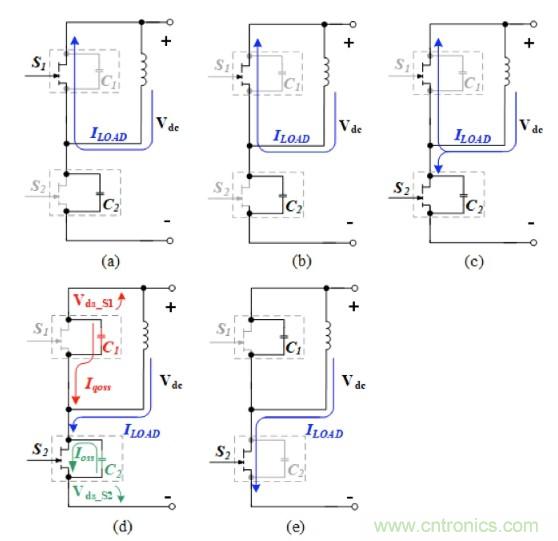

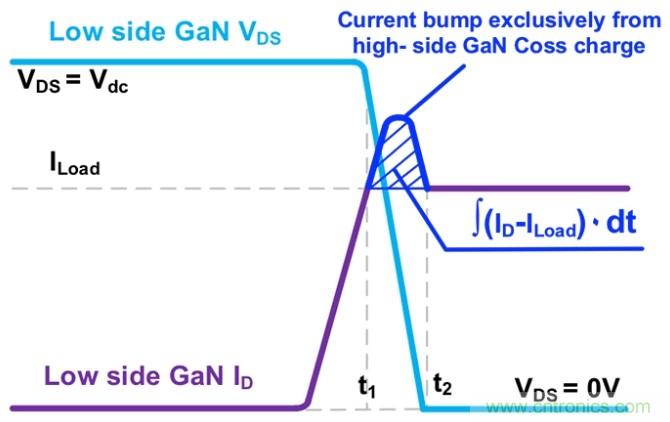

GaN半橋的典型硬開關(guān)開通過渡示意圖如圖3所示����,代表性的低壓側(cè)ID曲線如圖4所示���。在電壓換向期間(圖3d)�,S1上的電壓增加,S2上的電壓降低���。相應(yīng)地�����,晶體管漏極至源電容器C1和C2將分別充電和放電�����。由于S2的二維電子氣(2DEG)通道導(dǎo)通�,而S1的2DEG通道被關(guān)閉��,C1的充電電流流過S2����,導(dǎo)致電流突增。

圖3這些硬開關(guān)轉(zhuǎn)換圖顯示了S1導(dǎo)電(a)��、死區(qū)時(shí)間(b)����、電流換向(c)��、電壓換向(d)和S2導(dǎo)電(e)��。

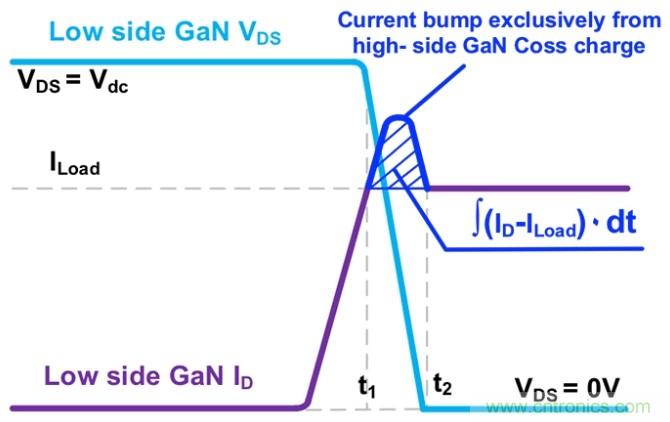

由于GaN晶體管不像Si和SiC mosfet�,沒有固有的體二極管�����,因此在電壓換向期間沒有反向恢復(fù)損耗(圖4中的t1~t2)��。低側(cè)漏極電流的緩沖區(qū)是來自相反開關(guān)S1的電容(COSS=CGD+CDS)充電電流IQ(OSS)的結(jié)果�����。

圖4這是低邊GaN晶體管的硬開關(guān)開啟過程�����。

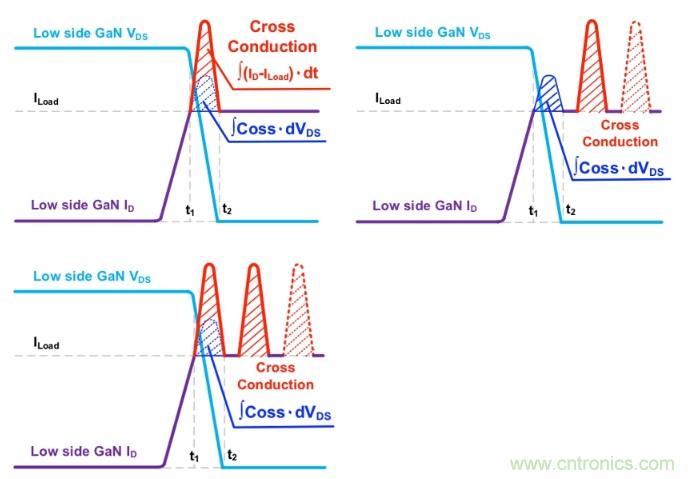

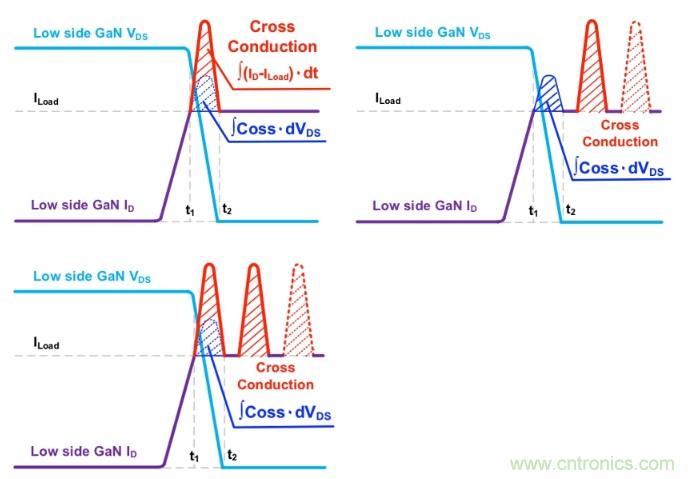

如果發(fā)生交叉?zhèn)鲗?dǎo)����,電流的碰撞面積將大于COSS的預(yù)期值�����。交叉?zhèn)鲗?dǎo)可以在電壓換向期間����、之后、期間和之后同時(shí)發(fā)生(圖5)�。

圖5在電壓換向期間、之后或兩者同時(shí)發(fā)生交叉?zhèn)鲗?dǎo)�。

推薦閱讀: