【導(dǎo)讀】設(shè)計人員有各種模數(shù)轉(zhuǎn)換器(ADC)可以選擇,數(shù)字?jǐn)?shù)據(jù)輸出類型是選擇過程中需要考慮的一項重要參數(shù)。目前,高速轉(zhuǎn)換器三種最常用的數(shù)字輸出是互補(bǔ)金屬氧化物半導(dǎo)體(CMOS)、低壓差分信號(LVDS)和電流模式邏輯(CML)。ADC中每種數(shù)字輸出類型都各有優(yōu)劣,設(shè)計人員應(yīng)根據(jù)特定應(yīng)用仔細(xì)考慮。這些因素取決于ADC的采樣速率和分辨率、輸出數(shù)據(jù)速率、系統(tǒng)設(shè)計的電源要求,以及其他因素。本文將討論每種輸出類型的電氣規(guī)格,及其適合特定應(yīng)用的具體特點(diǎn)。我們將從物理實(shí)現(xiàn)、效率以及最適合每種類型的應(yīng)用這些方面來對比這些不同類型的輸出。

CMOS數(shù)字輸出驅(qū)動器

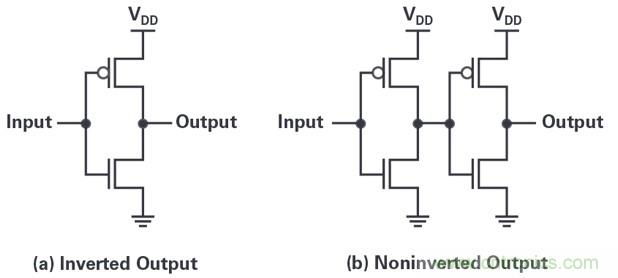

在采樣速率低于200 MSPS的ADC中,CMOS是很常見的數(shù)字輸出。典型的CMOS驅(qū)動器由兩個晶體管(一個NMOS和一個PMOS)組成,連接在電源(VDD)和地之間,如圖1a所示。這種結(jié)構(gòu)會導(dǎo)致輸出反轉(zhuǎn),因此,可以采用圖1b所示的背對背結(jié)構(gòu)作為替代方法,避免輸出反轉(zhuǎn)。輸出為低阻抗時,CMOS輸出驅(qū)動器的輸入為高阻抗。在驅(qū)動器的輸入端,由于柵極與導(dǎo)電材料之間經(jīng)柵極氧化層隔離,兩個CMOS晶體管的柵極阻抗極高。輸入端阻抗范圍可達(dá)k?至M?級。在驅(qū)動器輸出端,阻抗由漏電流ID控制,該電流通常較小。此時,阻抗通常小于幾百?。CMOS的電平擺幅大約在VDD和地之間,因此可能會很大,具體取決于VDD幅度。

圖1.典型CMOS數(shù)字輸出驅(qū)動器

由于輸入阻抗較高,輸出阻抗較低,CMOS的優(yōu)勢之一在于通??梢杂靡粋€輸出驅(qū)動多個CMOS輸入。CMOS的另一個優(yōu)勢是低靜態(tài)電流。唯一出現(xiàn)較大電流的情況是CMOS驅(qū)動器上發(fā)生切換時。無論驅(qū)動器處于低電平(拉至地)還是高電平(拉至VDD),驅(qū)動器中的電流都極小。但是,當(dāng)驅(qū)動器從低電平切換到高電平或從高電平切換到低電平時,VDD與地之間會暫時出現(xiàn)低阻抗路徑。該瞬態(tài)電流是轉(zhuǎn)換器速度超過200 MSPS時,輸出驅(qū)動器采用其他技術(shù)的主要原因。

轉(zhuǎn)換器的每一位也都需要CMOS驅(qū)動器。如果轉(zhuǎn)換器有14位,就需要14個CMOS輸出驅(qū)動器來傳輸這些位。一般會有一個以上的轉(zhuǎn)換器置于單個封裝中,常見為八個。采用CMOS技術(shù)時,意味著數(shù)據(jù)輸出需要高達(dá)112個輸出引腳。從封裝角度來看,這不太可能實(shí)現(xiàn),而且還會產(chǎn)生高功耗,并使電路板布局變得更加復(fù)雜。為了解決這些問題,我們引入了使用LVDS的接口。

LVDS數(shù)字輸出驅(qū)動器

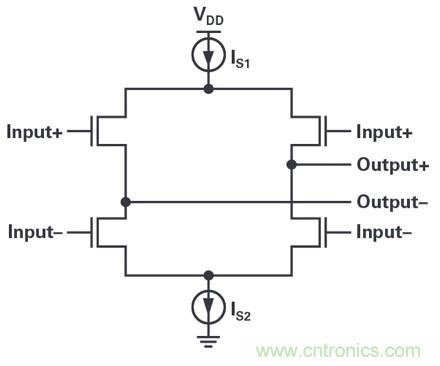

與CMOS技術(shù)相比,LVDS具備一些明顯優(yōu)勢。它可以在低電壓信號(約350 mV)下工作,并且為差分而非單端。低壓擺幅具有較快的切換時間,可以減少EMI問題。差分這一特性可以帶來共模抑制的好處。這意味著耦合到信號的噪聲對兩個信號路徑均為共模,大部分都可被差分接收器消除。LVDS中的阻抗必須更加嚴(yán)格控制。在LVDS中,負(fù)載阻抗應(yīng)約為100 ?,通常通過LVDS接收器上的并聯(lián)端接電阻實(shí)現(xiàn)。此外,LVDS信號還應(yīng)采用受控阻抗傳輸線進(jìn)行傳輸。差分阻抗保持在100 ?時,所需的單端阻抗為50 ?。圖2所示為典型LVDS輸出驅(qū)動器。

圖2.典型LVDS輸出驅(qū)動器

如圖2中LVDS輸出驅(qū)動器拓?fù)浣Y(jié)構(gòu)所示,電路工作時輸出電源會產(chǎn)生固定的直流負(fù)載電流。這可以避免輸出邏輯狀態(tài)躍遷時典型CMOS輸出驅(qū)動器中出現(xiàn)的電流尖峰。電路中的標(biāo)稱源電流/吸電流設(shè)為3.5 mA,使得端接電阻100 ?時典型輸出電壓擺幅為350 mV。電路的共模電平通常設(shè)為1.2 V,兼容3.3 V、2.5V和1.8 V電源電壓。

有兩種書面標(biāo)準(zhǔn)可用來定義LVDS接口。最常用的標(biāo)準(zhǔn)是ANSI/TIA/EIA-644規(guī)格,標(biāo)題為《低壓差分信號(LVDS)接口電路的電氣特性》。另一種是IEEE標(biāo)準(zhǔn)1596.3,標(biāo)題為《可擴(kuò)展一致性接口(SCI)的低壓差分信號IEEE標(biāo)準(zhǔn)》。

LVDS需要特別注意信號路由的物理布局,但在采樣速率達(dá)到200 MSPS或更高時可以為轉(zhuǎn)換器提供許多優(yōu)勢。LVDS的恒定電流使得可以支持許多輸出,無需CMOS要求的大量電流吸取。此外,LVDS還能以雙倍數(shù)據(jù)速率(DDR)模式工作,其中兩個數(shù)據(jù)位可以通過同一個LVDS輸出驅(qū)動器。與CMOS相比,可以減少一半的引腳數(shù)。此外,還降低了等量數(shù)據(jù)輸出的功耗。對轉(zhuǎn)換器數(shù)據(jù)輸出而言,LVDS確實(shí)相比CMOS具有諸多優(yōu)勢,但也和CMOS一樣存在一些限制。隨著轉(zhuǎn)換器分辨率的增加,LVDS接口所需的數(shù)據(jù)輸出量會變得更難針對PCB布局進(jìn)行管理。另外,轉(zhuǎn)換器的采樣率最終會使接口所需的數(shù)據(jù)速率超出LVDS的能力。

CML輸出驅(qū)動器

轉(zhuǎn)換器數(shù)字輸出接口的最新趨勢是使用具有電流模式邏輯(CML)輸出驅(qū)動器的串行接口。通常,高分辨率(≥14位)、高速(≥200 Msps)和需要小型封裝與低功耗的轉(zhuǎn)換器會使用這些類型的驅(qū)動器。CML輸出驅(qū)動器用在JESD204接口,這種接口目前用于最新轉(zhuǎn)換器。采用具有JESD204接口的CML驅(qū)動器后,轉(zhuǎn)換器輸出端的數(shù)據(jù)速率可達(dá)12 Gbps(當(dāng)前版本JESD204B規(guī)格)。此外,需要的輸出引腳數(shù)也會大幅減少。時鐘內(nèi)置于8b/10b編碼數(shù)據(jù)流,因此無需傳輸獨(dú)立時鐘信號。數(shù)據(jù)輸出引腳數(shù)量也得以減少,最少只需兩個。隨著轉(zhuǎn)換器的分辨率、速度和通道數(shù)的增加,數(shù)據(jù)輸出引腳數(shù)可能會相應(yīng)調(diào)整,以滿足所需的更高吞吐量。但是,由于使用CML驅(qū)動器采用的接口通常是串行接口,引腳數(shù)的增加與CMOS或LVDS相比要少得多(在CMOS或LVDS中傳輸?shù)臄?shù)據(jù)是并行數(shù)據(jù),需要的引腳數(shù)多得多)。

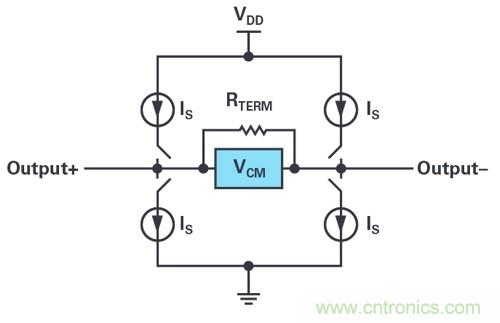

CML驅(qū)動器用于串行數(shù)據(jù)接口,因此,所需引腳數(shù)要少得多。圖3所示為用于具有JESD204接口或類似數(shù)據(jù)輸出的轉(zhuǎn)換器的典型CML驅(qū)動器。該圖顯示了CML驅(qū)動器典型架構(gòu)的一般情況。其顯示可選源終端電阻和共模電壓。電路的輸入可將開關(guān)驅(qū)動至電流源,電流源則將適當(dāng)?shù)倪壿嬛凋?qū)動至兩個輸出端。

圖3.典型CML輸出驅(qū)動器

CML驅(qū)動器類似于LVDS驅(qū)動器,以恒定電流模式工作。這也使得CML驅(qū)動器在功耗方面具備一定優(yōu)勢。在恒定電流模式下工作需要較少的輸出引腳,總功耗會降低。與LVDS一樣,CML也需要負(fù)載端接、單端阻抗為50 ?的受控阻抗傳輸線路,以及100 ?的差分阻抗。驅(qū)動器本身也可能具有如圖3所示的端接,對因高帶寬信號靈敏度引起的信號反射有所幫助。對采用JESD204標(biāo)準(zhǔn)的轉(zhuǎn)換器而言,差分和共模電平均存在不同規(guī)格,具體取決于工作速度。工作速度高達(dá)6.375 Gbps,差分電平標(biāo)稱值為800 mV,共模電平約為1.0 V。在高于6.375 Gbps且低于12.5 Gbps的速度下工作時,差分電平額定值為400 mV,共模電平仍約為1.0 V。隨著轉(zhuǎn)換器速度和分辨率增加,CML輸出需要合適類型的驅(qū)動器提供必要速度,以滿足各種應(yīng)用中轉(zhuǎn)換器的技術(shù)需求。

數(shù)字時序——需要注意的事項

每種數(shù)字輸出驅(qū)動器都有時序關(guān)系,需要密切監(jiān)控。由于CMOS和LVDS有多種數(shù)據(jù)輸出,因此必須注意信號的路由路徑,以盡量減小偏斜。如果差別過大,可能就無法在接收器上實(shí)現(xiàn)合適的時序。此外,時鐘信號也需要通過路由傳輸,并與數(shù)據(jù)輸出保持一致。時鐘輸出和數(shù)據(jù)輸出之間的路由路徑也必須格外注意,以確保偏斜不會太大。

在采用JESD204接口的CML中,還必須注意數(shù)字輸出之間的路由路徑。需要管理的數(shù)據(jù)輸出大大減少,因此,這一任務(wù)比較容易完成,但也不能完全忽略。這種情況下,由于時鐘內(nèi)置于數(shù)據(jù)中,因此無需擔(dān)心數(shù)據(jù)輸出和時鐘輸出之間的時序偏斜。但是,必須注意,接收器中要有合適的時鐘和數(shù)據(jù)恢復(fù)(CDR)電路。

除了偏斜之外,還必須關(guān)注CMOS和LVDS的建立和保持時間。數(shù)據(jù)輸出必須在時鐘邊沿躍遷之前的充足時間內(nèi)驅(qū)動到適當(dāng)?shù)倪壿嫚顟B(tài),并且必須在時鐘邊沿躍遷之后以這種邏輯狀態(tài)維持充足時間。這可能會受到數(shù)據(jù)輸出和時鐘輸出之間偏斜的影響,因此,保持良好的時序關(guān)系非常重要。由于具有較低信號擺幅和差分信號,LVDS相比CMOS具有一定優(yōu)勢。和CMOS驅(qū)動器一樣切換邏輯狀態(tài)時,LVDS輸出驅(qū)動器無需將這樣的大信號驅(qū)動至各種不同輸出,也不會從電源吸取大量電流。因此,它在切換邏輯狀態(tài)時不太可能會出現(xiàn)問題。如果有許多CMOS驅(qū)動器同時切換,電源電壓可能會下降,將正確的邏輯值驅(qū)動到接收器時會出現(xiàn)問題。LVDS驅(qū)動器會保持在恒定電流水平,這一特別問題就不會發(fā)生。此外,由于采用了差分信號,LVDS驅(qū)動器本身對共模噪聲的耐受能力也較強(qiáng)。CML驅(qū)動器具有和LVDS同樣的優(yōu)勢。這些驅(qū)動器也有恒定水平的電流,但和LVDS不同的是,由于數(shù)據(jù)為串行,所需電流值較小。此外,由于也采用了差分信號,CML驅(qū)動器同樣對共模噪聲具有良好的耐受能力。

隨著轉(zhuǎn)換器技術(shù)的發(fā)展,速度和分辨率不斷增加,數(shù)字輸出驅(qū)動器也不斷演變發(fā)展,以滿足數(shù)據(jù)傳輸需求。隨著轉(zhuǎn)換器中的數(shù)字輸出接口轉(zhuǎn)換為串行數(shù)據(jù)傳輸,CML輸出越來越普及。但是,目前的設(shè)計中仍然會用到CMOS和LVDS數(shù)字輸出。每種數(shù)字輸出都有最適合的應(yīng)用。每種輸出都面臨著挑戰(zhàn),必須考慮到一些設(shè)計問題,且各有所長。在采樣速度小于200 Msps的轉(zhuǎn)換器中,CMOS仍然是一種合適的技術(shù)。當(dāng)采樣速率增加到200 MSPS以上時,與CMOS相比,LVDS在許多應(yīng)用中更加可行。為了進(jìn)一步增加效率、降低功耗、減小封裝尺寸,CML驅(qū)動器可與JESD204之類的串行數(shù)據(jù)接口配合使用。

參考文獻(xiàn)

Bloomingdale、Cindy和Gary Hendrickson。AN-586應(yīng)用筆記:高速模數(shù)轉(zhuǎn)換器的LVDS數(shù)據(jù)輸出。ADI公司,2002年。

JEDEC標(biāo)準(zhǔn):JESD204(2006年4月)。JEDEC固態(tài)技術(shù)協(xié)會。

JEDEC標(biāo)準(zhǔn):JESD204A(2008年4月)。JEDEC固態(tài)技術(shù)協(xié)會。

JEDEC標(biāo)準(zhǔn):JESD204B(2011年7月)。JEDEC固態(tài)技術(shù)協(xié)會。

作者簡介

Jonathan Harris是ADI公司高速轉(zhuǎn)換器部門(位于北卡羅萊納州格林斯博羅)的產(chǎn)品應(yīng)用工程師。他在射頻行業(yè)從事產(chǎn)品支持工作超過7年。Jonathan擁有奧本大學(xué)電子工程碩士學(xué)位和北卡羅來納大學(xué)夏洛特分校電子工程學(xué)士學(xué)位。

推薦閱讀: