【導(dǎo)讀】晶振輸出串電阻就來自于最小化設(shè)計(jì),對(duì)于數(shù)字電路里最重要的時(shí)鐘源部分,應(yīng)該特別注意保證信號(hào)完整性,最小化設(shè)計(jì)中晶振外圍電路除了電阻還要有一些其他器件。

晶振輸出串電阻就來自于最小化設(shè)計(jì),對(duì)于數(shù)字電路里最重要的時(shí)鐘源部分,應(yīng)該特別注意保證信號(hào)完整性,最小化設(shè)計(jì)中晶振外圍電路除了電阻還要有一些其他器件。

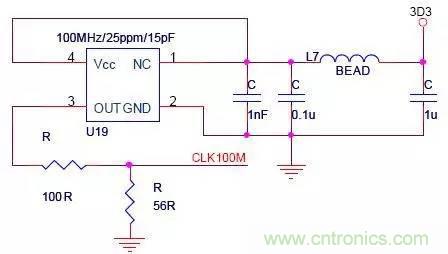

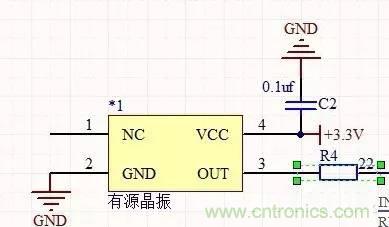

上圖中不僅考慮阻抗匹配,同時(shí)考慮電平匹配。L7為磁珠。

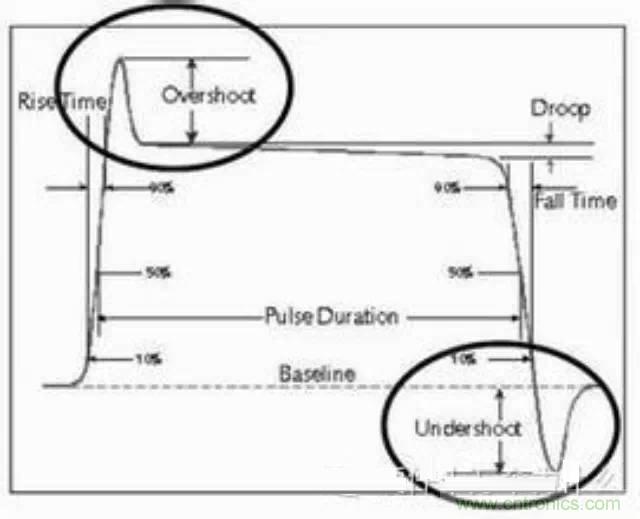

串電阻是為了減小反射波,避免反射波疊加引起過沖。有時(shí),不同批次的板子特性不一樣,留個(gè)電阻位置便于調(diào)整板子狀態(tài)到最佳。如無必要串電阻,就用0歐電阻連接。反射波在大部分電路里有害,但PCI卻恰恰利用了反射波形成有效信號(hào)。

一、減少諧波,有源晶體輸出的是方波,這將引起諧波干擾,尤其是阻抗嚴(yán)重不匹配的情況下,加上電阻后,該電阻將與輸入電容構(gòu)成RC積分平滑電路,將方波轉(zhuǎn)換為近似正弦波,雖然信號(hào)的完整性受到一定影響,但由于該信號(hào)還要經(jīng)過后級(jí)放大、整形后才作為時(shí)鐘信號(hào),因此,性能并不受影響,該電阻的大小需要根據(jù)輸入端的阻抗、輸入等效電容,有源晶體的輸出阻抗等因素選擇。

二、阻抗匹配,減小回波干擾及導(dǎo)致的信號(hào)過沖。我們知道,只要阻抗不匹配,都會(huì)產(chǎn)生信號(hào)反射,即回波,有源晶體的輸出阻抗通常都很低,一般在幾百歐以下,而信號(hào)源的輸入端在芯片內(nèi)部結(jié)構(gòu)上通常是運(yùn)放的輸入端,由芯片的內(nèi)部電路與外部的無源石英晶體構(gòu)成諧振電路(使用有源晶體后就不需要這個(gè)晶體了),這個(gè)運(yùn)放的輸出阻抗都在兆歐以上。

源端串接和接收端并接的匹配方式是不一樣的。

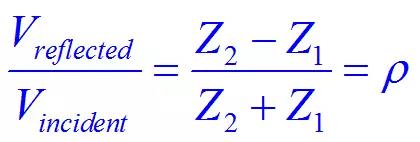

反射系數(shù),即

X=(Z2-Z1)/(Z1+Z2)

Z1和Z2分別為傳輸線阻抗失配分界面前后的瞬時(shí)阻抗。

那么這就有3種情況

1.Z1=Z2,即阻抗相等,X=0,即沒有反射

2.Z2=無窮大,X=1,即完全正反射,很多接收端的情況

3.Z2=0,X=-1,即完全負(fù)反射,末端短路了,接地了,阻抗為0,反射信號(hào)即可以理解為返回路徑上的回流

源端串聯(lián)電阻R,和驅(qū)動(dòng)端的源電阻R0,串聯(lián)后的總電阻R+R0,總電阻值等于或者最接近傳輸線阻抗Z。那么這時(shí)候信號(hào)分壓,真正進(jìn)入傳輸線上傳播的只有源信號(hào)電壓的一半,到接收端時(shí),由于接收端阻抗為無窮大,發(fā)生反射,反射系數(shù)為1,傳輸系數(shù)Y=2,即進(jìn)入接收端的信號(hào)又等于驅(qū)動(dòng)端的信號(hào)了。而返回源端的信號(hào)因?yàn)樽杩箾]有變化,到源端時(shí)被源電阻和串聯(lián)匹配電阻吸收了,不再發(fā)生反射,這是理想情況。

單一網(wǎng)絡(luò)SI的主要問題就是反射,但是這又是一個(gè)比較大的話題,牽涉到阻抗匹配,拓?fù)浣Y(jié)構(gòu),端接等等,所以想說的比較透徹似乎不太容易,盡量吧

一.反射產(chǎn)生原理

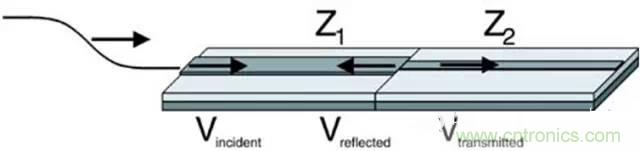

先來看上面的圖,信號(hào)在傳輸線中傳輸,從Z1到Z2的過程中,阻抗發(fā)生變化,部分信號(hào)將沿著與原傳播方向相反的方向反射,而另一部分將繼續(xù)傳播,但幅度有所改變。將瞬時(shí)阻抗發(fā)生改變的地方稱為阻抗突變,反射信號(hào)的大小由瞬時(shí)阻抗的突變程度確定,在理論分析中,我們用反射系數(shù)來表示

兩個(gè)區(qū)域的阻抗差異越大,反射信號(hào)強(qiáng)度就越大。例如,如果1V信號(hào)沿特性阻抗=50W的線網(wǎng)傳播,受到的瞬時(shí)阻抗=50W,當(dāng)它進(jìn)入特性阻抗為75W的區(qū)域時(shí),反射系數(shù)為(75-50)/(75+50)= 20%,反射電壓為20%×1V= 0.2V

我們可以從理論上對(duì)上面的公式進(jìn)行推導(dǎo),但此處不再贅述,有興趣的話可以參考相關(guān)資料

在實(shí)際的工程中,反射不可能完全消除,SI工程師所要做的就是盡量減少反射對(duì)信號(hào)的影響,反射的根源是阻抗不匹配,所以減小反射最有效的途徑就是端接,端接方法的選擇,終端電阻的選取,都對(duì)。

根據(jù)反射系數(shù)的公式,我們可以得出三種最典型的情況:開路,短路,匹配

1.Z1=Z2,即阻抗相等,ρ=0,即沒有反射

2.Z2=無窮大,ρ=1,即完全正反射,這意味這在開路短產(chǎn)生與入射波大小相同,方向相反,返回源端的反射波,如果測(cè)量開路端得電壓,將得到兩個(gè)電壓之和

3.Z2=0,ρ=-1,即完全負(fù)反射,末端短路了,接地了,阻抗為0,反射信號(hào)即可以理解為返回路徑上的回流

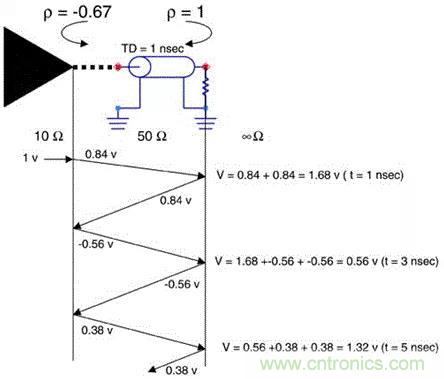

二.反彈圖

反射理論里面最重要的莫過于Lattice Diagrams,也就是我們說的反彈圖,有些資料也叫網(wǎng)格圖

我們知道,當(dāng)信號(hào)在傳輸線終端的阻抗不連續(xù)點(diǎn)被反射時(shí),信號(hào)的一部分將反射回源頭。當(dāng)反射信號(hào)到達(dá)源頭時(shí),若源頭端阻抗不等于傳輸線阻抗就將產(chǎn)生二次反射。接著,若傳輸線的兩端都存在阻抗不連續(xù),信號(hào)將在驅(qū)動(dòng)線路和接收線路之間來回反射,直到最后達(dá)到直流穩(wěn)態(tài)。

下面,我們來分析這種情況。如果已知驅(qū)動(dòng)器的源電壓、傳輸線時(shí)延TD、信號(hào)沿途各區(qū)域的阻抗,就可以計(jì)算出每個(gè)交界面的反射,并計(jì)算出每一點(diǎn)的實(shí)時(shí)電壓。

例如,已知源電壓是1V,內(nèi)阻是10Ω,則實(shí)際進(jìn)入時(shí)延為1ns 50Ω傳輸線的電壓是1V×50/(10+50)=0.84V。這個(gè)0.84V信號(hào)就是沿傳輸線傳播的初始入射電壓。

1ns后在線末端,假設(shè)傳輸線末端開路,反射系數(shù)為1,開路端的總電壓為兩個(gè)波之和,即0.84V+0.84V=1.68V。

再經(jīng)過1ns后,0.84V反射波到達(dá)源端,又一次遇到阻抗突變。源端的反射系數(shù)是(10 - 50)/(10+50)=- 0.67,這時(shí)將有0.84V×(-0.67)=-0.56V反射回線遠(yuǎn)端。

這個(gè)新產(chǎn)生的波在遠(yuǎn)端又會(huì)被反射,即-0.56V電壓將被反射。這樣,線遠(yuǎn)端開路處將同時(shí)有四個(gè)波存在:從一次行波中得到2×0.84 V=1.68 V,從二次反射中得到的2×(-0.56)=-1.12 V,故總電壓為0.56 V。

-0.56V信號(hào)到達(dá)源端后仍然會(huì)再次反射,反射電壓是+0.38 V。在遠(yuǎn)端新的時(shí)刻,總電壓0.56V + 0.38V + 0.38V=1.32V

把上面的計(jì)算用圖形來表示的話,就得到了我們所說的反彈圖

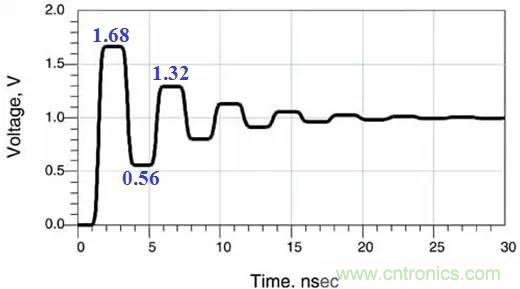

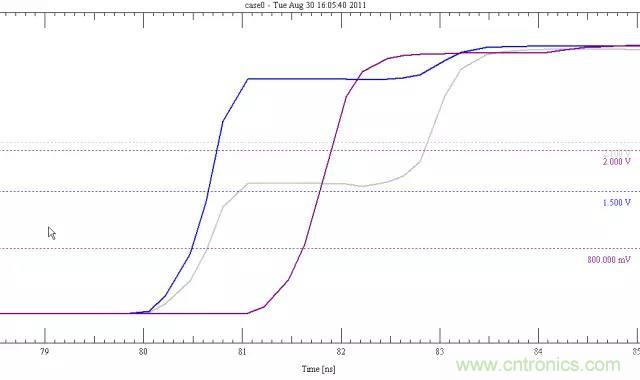

時(shí)域信號(hào)波形的表現(xiàn)如下圖:

圖中有兩個(gè)重要的特性:

1. 遠(yuǎn)端的電壓最終逼近源電壓1V,因?yàn)樵撾娐肥情_路的。這是一個(gè)必然的結(jié)果——源電壓最終是加在開路上。

2.開路處的實(shí)際電壓有時(shí)大于源電壓。源電壓僅1V,然而遠(yuǎn)端測(cè)得的最大電壓是1.68V。高出的電壓是由于傳輸線分布參數(shù)L、C諧振產(chǎn)生的。

三.反射什么時(shí)候發(fā)生

那么,反射什么時(shí)候發(fā)生呢?這的確是一個(gè)值得探討的問題,前面,我們提過,反射由阻抗突變而起,而且阻抗改變的長度也有關(guān)系,下面我們通過簡單的仿真來驗(yàn)證下這個(gè)問題

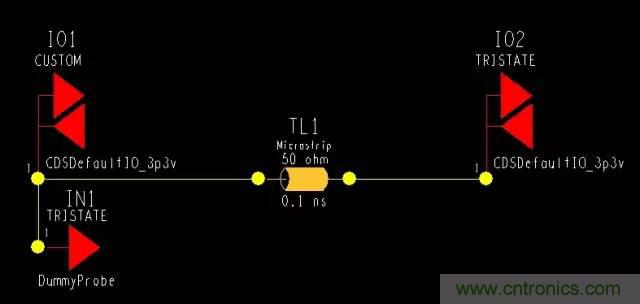

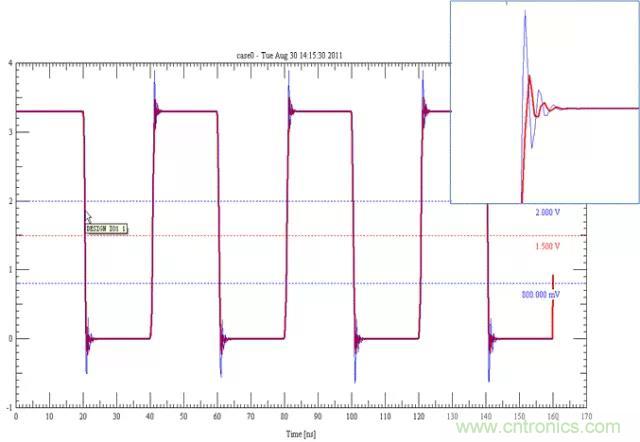

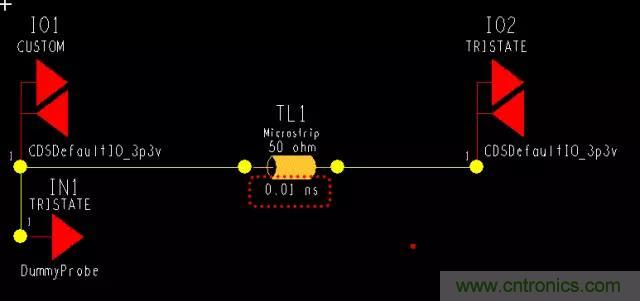

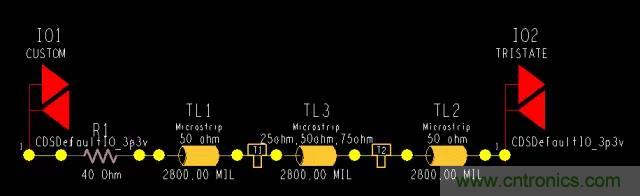

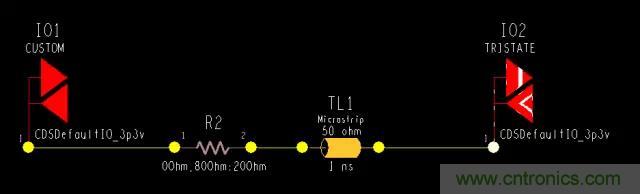

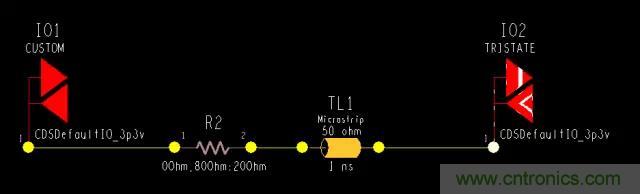

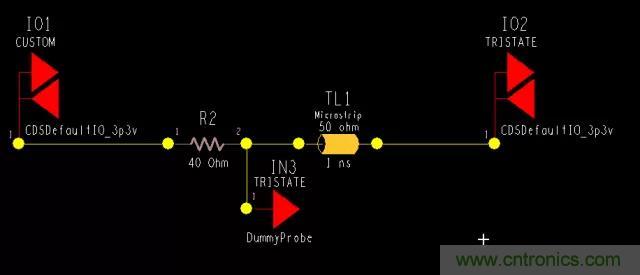

首先,我們?cè)赟igXplorer中搭建一個(gè)簡易的Point-Point拓?fù)浣Y(jié)構(gòu),開始時(shí)對(duì)驅(qū)動(dòng)端的源電阻不得而知,使用理想傳輸線,特征阻抗為50ohm,傳輸延時(shí)為0.1ns,未加任何阻抗匹配元件,仿真頻率選擇50Mhz

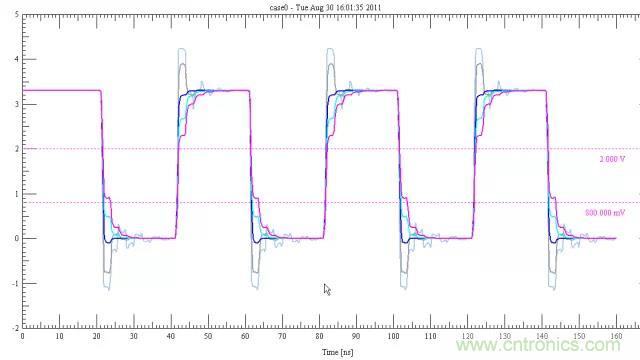

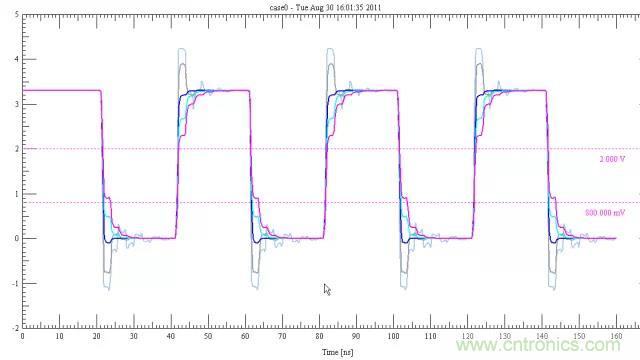

仿真波形如下,可以看到,在驅(qū)動(dòng)端和接收端都有比較大的振鈴

從上面的仿真結(jié)果看,源端內(nèi)阻抗和傳輸線阻抗不匹配的確造成的反射,產(chǎn)生了過沖并生成了振鈴,這時(shí)我們就猜想這一切的產(chǎn)生是否和傳輸線的長度有關(guān)系呢?下面修改傳輸線延時(shí)為0.01ns

這時(shí)候會(huì)發(fā)現(xiàn)剛才的振鈴和過沖都消失了

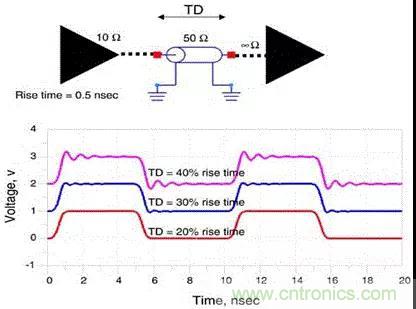

仿真頻率仍然為50Mhz,看下仿真波形,驚訝地看到那些毛刺不見了,接收端和驅(qū)動(dòng)端的波形接近重合,似乎沒有發(fā)生一點(diǎn)變形。到這里有人也許會(huì)下這樣的結(jié)論,傳輸線足夠短的時(shí)候,就不發(fā)生反射了。那么,到底多短的時(shí)候才會(huì)沒有反射呢?這里直接引用Eric博士的研究結(jié)果:

當(dāng)TD<上升邊的20%時(shí),振鈴可以忽略,傳輸線不需要匹配(即線較短的電小尺寸時(shí))

在 FR4中(前提),信號(hào)傳播速度大約為6in/ns。如果上升邊是1ns,終端沒有匹配的傳輸線最大允許長度約為6 in/ns×0.2ns=1.2 in。

一個(gè)易記的經(jīng)驗(yàn)法則是:為避免信號(hào)完整性出問題,沒有終端匹配的FR4傳輸線最大容許長度約為:

其中:Lenmax 沒有終端匹配的傳輸線最大允許長度,單位in

RT 信號(hào)上升邊,單位ns

經(jīng)驗(yàn)法則:沒有終端匹配的傳輸線最大允許長度的英寸(inch)值等于信號(hào)上升邊的納秒(ns)值。

也就是說,如果上升時(shí)間是1 ns,則沒有終端端接的傳輸線的最大長度約為1 in,如果上升時(shí)間為0.1 ns,則最大長度為0.1 in.

上面的經(jīng)驗(yàn)公式是一個(gè)非常有用的經(jīng)驗(yàn)公式,它可以用于各種不同的情況中,比如阻抗突變的長度,比如短樁線的長度對(duì)反射的影響

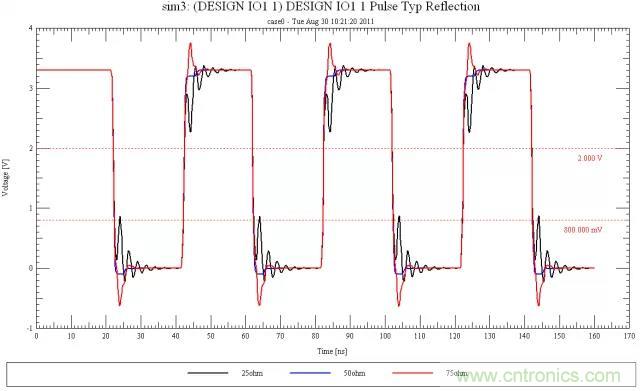

比如在實(shí)際的Layout中,我們希望所有傳輸線的阻抗是一樣的,但是有時(shí)候傳輸線經(jīng)過BGA的時(shí)候,不可避免的需要改變線寬,所以阻抗也跟著就改變了,那么阻抗的改變對(duì)信號(hào)的影響如何呢,繼續(xù)看仿真結(jié)果

可以看到,當(dāng)突變的阻抗(TL3)大于特性阻抗時(shí),信號(hào)會(huì)有一個(gè)向上的過沖,當(dāng)突變的阻抗小于特性阻抗時(shí),信號(hào)會(huì)有一個(gè)向下的過沖, 那么,按照上面的分析,是不是如果TL3長度足夠短時(shí),反射就可以消除呢,答案是肯定的

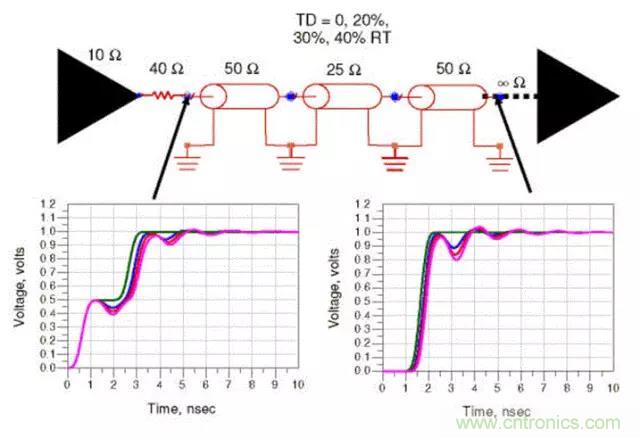

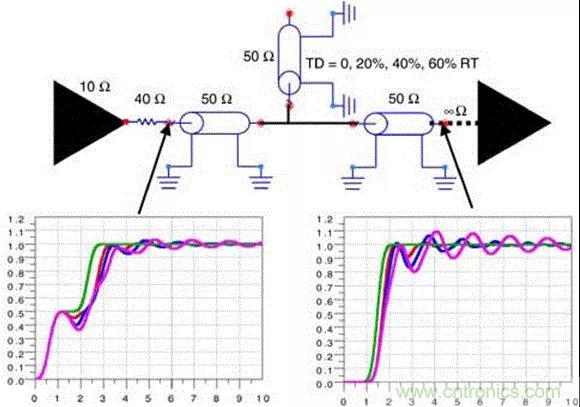

上面的圖為傳輸線上有25Ω短突變時(shí)的反射信號(hào)和傳輸信號(hào)。如果突變段的時(shí)延小于信號(hào)上升邊20%,就不會(huì)造成問題,從而,得到了與前面相同的經(jīng)驗(yàn)法則,即可允許的阻抗突變最大長度為

經(jīng)驗(yàn)法則:突變段的長度(in)應(yīng)小于信號(hào)上升邊(ns),此時(shí)可以忽略突變的影響。

同樣,可以得到短樁線的最小長度也滿足這個(gè)經(jīng)驗(yàn)公式

三.點(diǎn)對(duì)點(diǎn)拓?fù)涞亩私硬呗?/div>

上面雖然分析了阻抗突變傳輸線長度足夠短的時(shí)候,反射可以消除,但是在現(xiàn)在的設(shè)計(jì)中,幾乎所有互連線的長度都大于這個(gè)值,所以能至少在一端消除反射,就可以減小振鈴噪聲

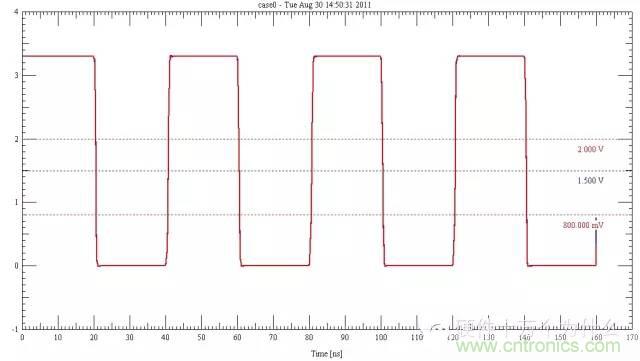

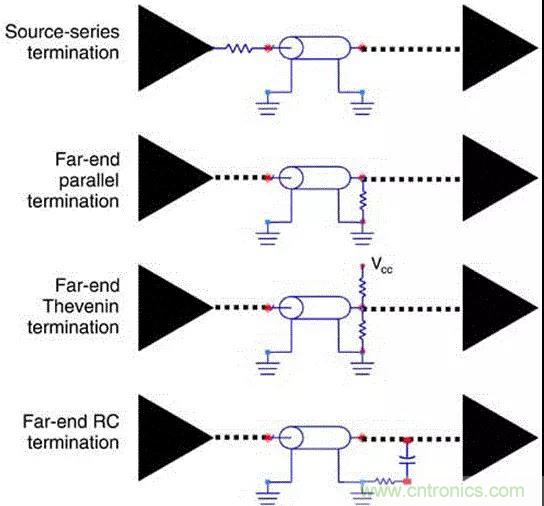

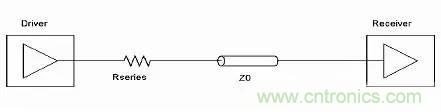

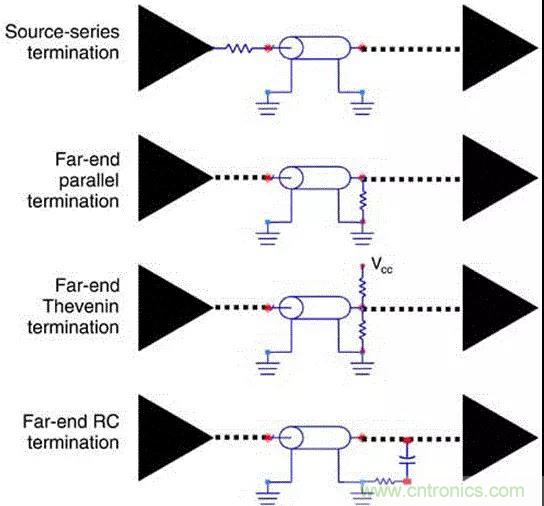

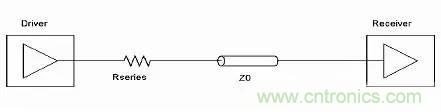

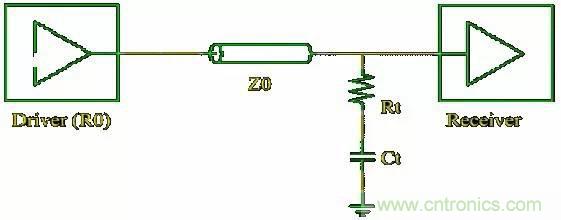

上圖是幾種常用的端接方式,第一種源端串聯(lián)端接是最常用的方法,下面來仿真一下

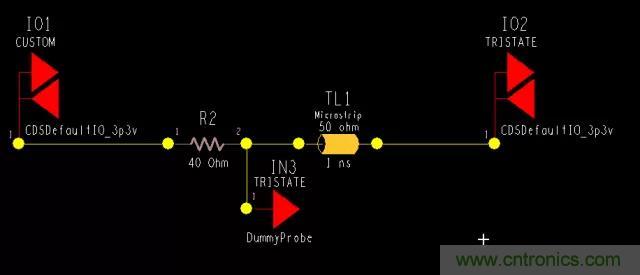

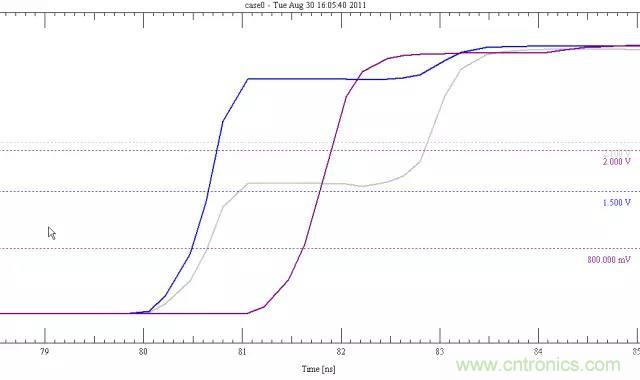

因?yàn)榇蟛糠謺r(shí)候,我們并不知道Source 芯片內(nèi)部的內(nèi)阻,所以,串聯(lián)電阻的值也只能通過仿真或者嘗試的辦法得到,如上圖,我們?cè)O(shè)置R2的值為0~80 Ohm,步進(jìn)為20,可以得到下面的波形,過沖最高的為0ohm, 而40ohm 的波形(藍(lán)色)是最接近理想情況的。

但是加入電阻以后呢,從TL1看進(jìn)去,入射電壓就等于由R2分壓的電壓,如果完美匹配的話,就是原電壓的1/2, 通過波形來看一下,R2.2 端得波形如下圖灰色的信號(hào)所示,它在一定的時(shí)間內(nèi)有一個(gè)臺(tái)階,幅度為原電壓的一半,持續(xù)時(shí)間為2倍的傳輸延時(shí),這也就是為什么在實(shí)際的測(cè)試中,在輸出端測(cè)出的波形經(jīng)常會(huì)有一個(gè)臺(tái)階的原因

簡易阻抗匹配方法

在高速的設(shè)計(jì)中,阻抗的匹配與否關(guān)系到信號(hào)的質(zhì)量優(yōu)劣。阻抗匹配的技術(shù)可以說是豐富多樣,在此只對(duì)幾種簡單常用的端接方法進(jìn)行介紹。為什么要進(jìn)行阻抗匹配呢?無外乎幾種原因,如減少反射、控制信號(hào)邊沿速率、減少信號(hào)波動(dòng)、一些電平信號(hào)本身需要等等。

端接阻抗匹配一般有5種方法:

1.源端串聯(lián)匹配,

2.終端并聯(lián)匹配,

3.戴維南匹配,

4.RC網(wǎng)絡(luò)匹配,

5.二極管匹配。

1.串聯(lián)端接匹配:

一般多在源端使用,Rs(串聯(lián)電阻) = Z0(傳輸線的特性阻抗)- R0(源阻抗)。例如:若R0為22,Z0為55Ω,則Rs應(yīng)為33Ω。

優(yōu)點(diǎn):

①器件單一;

②抑制振鈴,減少過沖;

③適用于集總線型負(fù)載和單一負(fù)載;

④增強(qiáng)信號(hào)完整性,產(chǎn)生更小EMI。

缺點(diǎn):

①當(dāng)TTL,CMOS器件出現(xiàn)在相同網(wǎng)絡(luò)時(shí),串聯(lián)匹配不是最佳選擇;

②分布式負(fù)載不是適用,因?yàn)樵谧呔€路徑的中間,電壓僅是源電壓的一半;

③接收端的反相反射仍然存在;

④影響信號(hào)上升時(shí)間并增加信號(hào)延時(shí)。

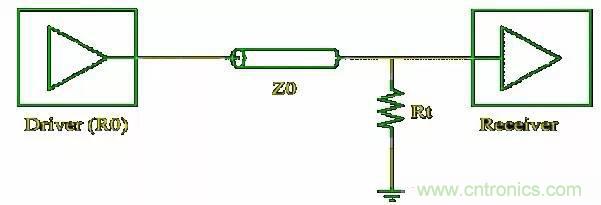

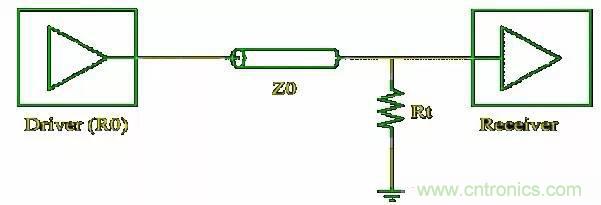

2.并聯(lián)端接匹配:

此Rt電阻值必須等于傳輸線所要求的電阻值,電阻的一端接信號(hào),一端接地或電源。簡單的終端并聯(lián)匹配一般不用于TTL,COMS電路,因?yàn)樵诟哌壿嫚顟B(tài)時(shí),此方法需要較大的驅(qū)動(dòng)電流。

優(yōu)點(diǎn):

①器件單一;

②適用于分布式負(fù)載;

③反射幾乎可以完全消除;

④電阻阻值易于選擇。

缺點(diǎn):

①此電阻需要驅(qū)動(dòng)源端的電流驅(qū)動(dòng),增加系統(tǒng)電路的功耗;

②降低噪聲容限。

此電阻值必須等于傳輸線所要求的電阻值。電阻的一端接信號(hào),一端接地。簡單的終端并聯(lián)匹配一般不用于TTL,COMS電路,因?yàn)樗麄儫o法提供強(qiáng)大的輸出電流。

3.戴維南端接匹配:

一個(gè)電阻上拉,一個(gè)電阻下拉,通常采用 R1/R2 = 220/330的比值。戴維南等效阻抗必須等于走線的特性阻抗。對(duì)于大多數(shù)設(shè)計(jì)R1>R2,否則TTL/COMS電路將無法工作。

優(yōu)點(diǎn):

①適用于分布式負(fù)載;

②完全吸收發(fā)送波,消除反射。

缺點(diǎn):

①增加系統(tǒng)電路的功耗;

②降低噪聲容限;

③使用兩個(gè)電阻,增加布局、布線難度;

④電阻值不易于選擇。

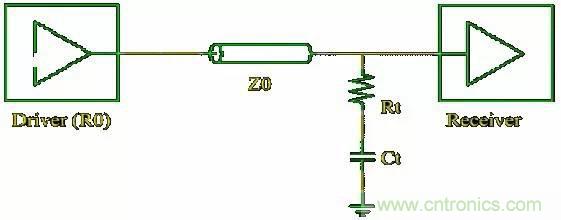

4.RC網(wǎng)絡(luò)匹配:

電阻與電容相連,電阻另一端接信號(hào),電容另一端接地。電阻應(yīng)等于走線特性阻抗,容值通常較小(20pF-600pF)。對(duì)差分信號(hào)只需三個(gè)原件,兩個(gè)電阻加一個(gè)電容。

優(yōu)點(diǎn):

①適用于分布式及總線型負(fù)載;

②完全吸收發(fā)送波,消除反射;

③具有很低的直流功率損耗。

缺點(diǎn):

①會(huì)降低高速信號(hào)的速率,增加信號(hào)延時(shí);

②RC電路的時(shí)間常數(shù)會(huì)導(dǎo)致電路中存在反射;

③對(duì)于高頻、高速短路要慎用;

④使用兩個(gè)器件,增加布局、布線難度。

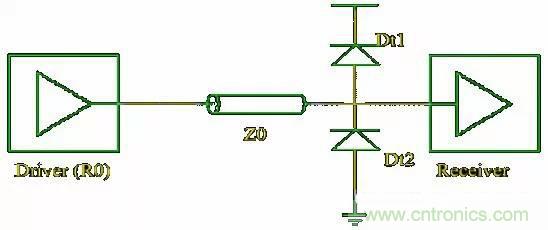

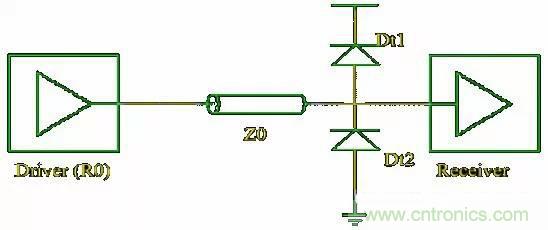

5.二極管端接匹配:

此端接常用于差分或成對(duì)網(wǎng)絡(luò),二極管常用于限制走線過程的過沖。

優(yōu)點(diǎn):

①預(yù)防輸入端的過沖。

缺點(diǎn):

①不能減少反射。

推薦閱讀: