【導(dǎo)讀】PCB板的設(shè)計中 ,隨著頻率的迅速提高 ,將出現(xiàn)與低頻 PCB板設(shè)計所不同的諸多干擾 ,并且 ,隨著頻率的提高和 PCB板的小型化和低成本化之間的矛盾日益突出 ,這些干擾越來越多也越來越復(fù)雜。在實際的研究中 ,我們歸納起來 ,主要有四方面的干擾存在,主要有電源噪聲、傳輸線干擾、耦合、電磁干擾(EMI)四個方面。通過分析高頻PCB的各種干擾問題,結(jié)合工作中實踐,提出了有效的解決方案。

1、電源噪聲

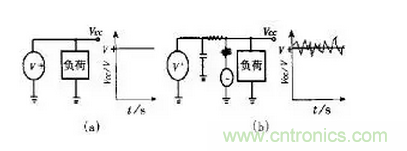

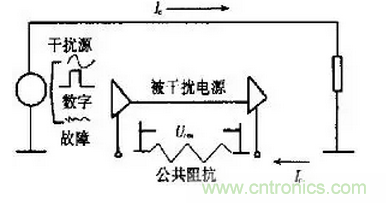

高頻電路中,電源所帶有的噪聲對高頻信號影響尤為明顯。因此,首先要求電源是低噪聲的。在這里,干凈的地和干凈的電源同樣重要,為什么呢?電源特性如圖1所示。很明顯,電源是具有一定阻抗的,并且阻抗是分布在整個電源上的,因此,噪聲也會疊加在電源上。那么我們就應(yīng)該盡可能地減小電源的阻抗,所以最好要有專有的電源層和接地層。在高頻電路設(shè)計中,電源以層的形式設(shè)計,在大多數(shù)情況下都比以總線的形式設(shè)計要好得多,這樣回路總可以沿著阻抗最小的路徑走。此外電源板還得為PCB上所有產(chǎn)生和接受的信號提供一個信號回路,這樣可以最小化信號回路,從而減小噪聲,這點常常為低頻電路設(shè)計人員所忽視。

圖1 電源特性

PCB設(shè)計中消除電源噪聲的方法有如下幾種。

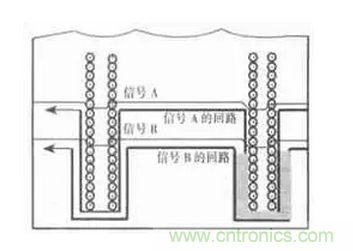

(1)注意板上通孔:通孔使得電源層上需要刻蝕開口以留出空間給通孔通過。而如果電源層開口過大,勢必影響信號回路,信號被迫繞開,回路面積增大,噪聲加大。同時如果一些信號線都集中在開口附近,共用這一段回路,公共阻抗將引發(fā)串?dāng)_。如圖2所示。

圖2 旁路信號回路的公共路徑

(2)連接線需要足夠多的地線:每一信號需要有自己的專有的信號回路,而且信號和回路的環(huán)路面積盡可能小,也就是說信號與回路要并行。

(3)模擬與數(shù)字電源的電源要分開:高頻器件一般對數(shù)字噪音非常敏感,所以兩者要分開,在電源的入口處接在一起,若信號要跨越模擬和數(shù)字兩部分的話,可以在信號跨越處放置一條回路以減小環(huán)路面積。用于信號回路的數(shù)模間的跨越如圖3 所示。

圖3 用于信號回路的數(shù)模間的跨越

(4)避免分開的電源在不同層間重疊:否則電路噪聲很容易通過寄生電容耦合過去。

(5)隔離敏感元件:如PLL。

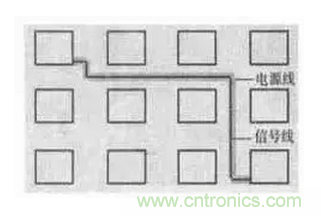

(6)放置電源線:為減小信號回路,通過放置電源線在信號線邊上來實現(xiàn)減小噪聲,如圖4所示。

圖4 信號線邊上放置電源線

2、傳輸線

在PCB中只可能出現(xiàn)兩種傳輸線:帶狀線和微波線,傳輸線最大的問題就是反射,反射會引發(fā)出很多問題,例如負(fù)載信號將是原信號與回波信號的疊加,增加信號分析的難度;反射會引起回波損耗(回?fù)p),其對信號產(chǎn)生的影響與加性噪聲干擾產(chǎn)生的影響同樣嚴(yán)重:

(1)信號反射回信號源會增加系統(tǒng)噪聲,使接收機更加難以將噪聲和信號區(qū)分開來;

(2)任何反射信號基本上都會使信號質(zhì)量降低,都會使輸入信號形狀上發(fā)生變化。大原則上來說,解決的辦法主要是阻抗匹配(例如互連阻抗應(yīng)與系統(tǒng)的阻抗非常匹配)但有時候阻抗的計算比較麻煩,可以參考一些傳輸線阻抗的計算軟件。

PCB設(shè)計中消除傳輸線干擾的方法如下:

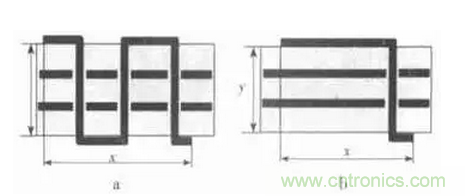

(a)避免傳輸線的阻抗不連續(xù)性。阻抗不連續(xù)的點就是傳輸線突變的點,如直拐角、過孔等,應(yīng)盡量避免。方法有:避免走線的直拐角,盡可能走45°角或者弧線,大彎角也可以;盡可能少用過孔,因為每個過孔都是阻抗不連續(xù)點,如圖5所示;外層信號避免通過內(nèi)層,反之亦然。

圖5 消除傳輸線干擾的方法

(b)不要用樁線。因為任何樁線都是噪聲源。如果樁線短,可在傳輸線的末端端接就可以了;如果樁線長,會以主傳輸線為源,產(chǎn)生很大的反射,使問題復(fù)雜化,建議不要使用。

3、耦合

(1)公共阻抗耦合:是一種常見的耦合通道即干擾源和被干擾設(shè)備往往共用某些導(dǎo)體(例如回路電源、總線、公共接地等),如圖6所示。

圖6 公共阻抗耦合

在該通道上,Ic的下降回在串聯(lián)的電流回路中引起共模電壓,影響接收機。

(2)場共模耦合將引起輻射源在由被干擾電路形成的環(huán)路和公共參考面上引起共模電壓。如果磁場占主要地位,在串聯(lián)地回路中產(chǎn)生的共模電壓的值是Vcm=-(△B/△t)*面積(式中的△B=磁感應(yīng)強度的變化量)如果是電磁場,已知它的電場值時,其感應(yīng)電壓:Vcm=(L*h*F*E)/48,公式適用于L(m)=150MHz以下,超過這個限制,最大感應(yīng)電壓的計算可簡化為:Vcm=2*h*E。

(3)差模場耦合:指直接的輻射被導(dǎo)線對或電路板上的引線及其回路所感應(yīng)接收.如果盡量靠近兩根導(dǎo)線。這種耦合會**減小,所以可以將兩根導(dǎo)線絞在一起來減小干擾。

(4)線間耦合(串?dāng)_)可以使任何線等于并聯(lián)電路間發(fā)生不希望有的耦合,嚴(yán)重的將**損害系統(tǒng)的性能。其種類可分為容性串?dāng)_和感性串?dāng)_。前者是因為線間的寄生電容使得噪聲源上的噪聲通過電流的注入耦合到噪聲接收線上;后者可以被想象成信號在一個不希望有的寄生變壓器初次級間的耦合。感性串?dāng)_的大小取決于兩個環(huán)路的靠近程度和環(huán)路面積的大小,及所影響的負(fù)載的阻抗。

(5)電源線耦合:是指交流或直流電源線受到電磁干擾后,電源線又將這些干擾

傳輸?shù)狡渌O(shè)備上。

PCB設(shè)計中消除串?dāng)_的方法有如下幾種:

兩種串?dāng)_的大小均隨負(fù)載阻抗的增大而增大,所以應(yīng)對由串?dāng)_引起的干擾敏感的信號線進行適當(dāng)?shù)亩私印?/div>

盡可能地增大信號線間的距離,可以有效地減少容性串?dāng)_。進行接地層管理,在布線之間進行間隔(例如對有源信號線和地線進行隔離,尤其在狀態(tài)發(fā)生跳變的信號線和地之間更要進行間隔)和降低引線電感。

在相鄰的信號線間**一根地線也可以有效減小容性串?dāng)_,這根地線需要每1/4波長就接入地層。

對于感性串?dāng)_,應(yīng)盡量減小環(huán)路面積,如果允許的話,消除這個環(huán)路。

避免信號共用環(huán)路。

關(guān)注信號完整性:設(shè)計者要在焊接過程中實現(xiàn)端接來解決信號完整性。采用這種辦法的設(shè)計者可專注屏蔽用銅箔的微帶長度,以便獲得信號完整性的良好性能。對于在通信結(jié)構(gòu)中采用密集連接器的系統(tǒng),設(shè)計者可用一塊PCB作端接。

4、電磁干擾

隨著速度的提升,EMI將變得越來越嚴(yán)重,并表現(xiàn)在很多方面上(例如互連處的電磁干擾),高速器件對此尤為敏感,它會因此接收到高速的假信號,而低速器件則會忽視這樣的假信號。

PCB設(shè)計中消除電磁干擾的方法有如下幾種:

減小環(huán)路:每個環(huán)路都相當(dāng)于一個天線,因此我們需要盡量減小環(huán)路的數(shù)量,環(huán)路的面積以及環(huán)路的天線效應(yīng)。確保信號在任意的兩點上只有唯一的一條回路路徑,避免人為環(huán)路,盡量使用電源層。

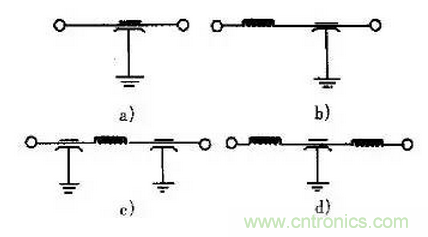

濾波:在電源線上和在信號線上都可以采取濾波來減小EMI,方法有三種:去耦電容、EMI濾波器、磁性元件。EMI濾波器如圖7所示。

圖7 濾波器的類型

屏蔽。由于篇幅問題再加上討論屏蔽的文章很多,不再具體介紹

盡量降低高頻器件的速度。

增加PCB板的介電常數(shù),可防止靠近板的傳輸線等高頻部分向外輻射;增加PCB板的厚度,盡量減小微帶線的厚度,可以防止電磁線的外溢,同樣可以防止輻射。

討論到此我們可以總結(jié)一下在高頻PCB設(shè)計中,我們應(yīng)該遵循下面的原則:

電源與地的統(tǒng)一,穩(wěn)定。

仔細(xì)考慮的布線和合適的端接可以消除反射。

仔細(xì)考慮的布線和合適的端接可以減小容性和感性串?dāng)_。

需要抑制噪聲來滿足EMC要求。

推薦閱讀: