【導(dǎo)讀】為了發(fā)掘宇航市場(chǎng)的潛力,衛(wèi)星運(yùn)營(yíng)商正通過提供增值服務(wù),如超高分辨率成像、流媒體視頻直播和星上人工智能,提升星上處理的能力以減少下行鏈路的需求。從2019年到2024年,高吞吐量載荷的市場(chǎng)需求預(yù)計(jì)增長(zhǎng)12倍,帶寬增加至26500 Gbps。

上述的所有應(yīng)用都和存儲(chǔ)器的容量和速度密切相關(guān)。實(shí)時(shí)存儲(chǔ)前向高吞吐量載荷基于支持GHz I/O速率的FPGA、存儲(chǔ)器、寬帶ADC和DAC。例如,一個(gè)12位1.5Gsps采樣率的ADC每秒產(chǎn)生18Gb的原始數(shù)據(jù)。一分鐘的壓縮SAR信息需要大約70Gb的存儲(chǔ)容量。這對(duì)現(xiàn)有的宇航級(jí)存儲(chǔ)器解決方案的I/O帶寬、訪問時(shí)間、功耗、物理尺寸和存儲(chǔ)容量提出了很大的挑戰(zhàn)。

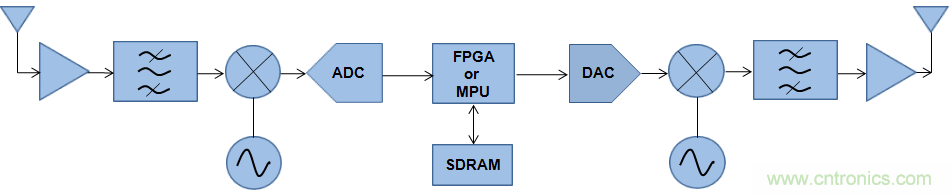

一個(gè)數(shù)字高吞吐量載荷的典型架構(gòu)如下圖所示。它需要使用一個(gè)宇航級(jí)FPGA或一個(gè)快速微處理器進(jìn)行星上處理。最新的超深亞微米工藝的經(jīng)過認(rèn)證的FPGA一般包含大約30Mb的片上存儲(chǔ)器,而CPU會(huì)更少?;谶@一架構(gòu)的電信、地球觀測(cè)和科學(xué)載荷多使用Xilinx的XQRKU060、Microchip的RTPolarFire或NanoXplore的宇航級(jí)FPGA,需要額外的快速片外存儲(chǔ)器存儲(chǔ)這些應(yīng)用產(chǎn)生的大量數(shù)據(jù)。

圖 1 : 數(shù)字高吞吐量載荷的架構(gòu)

實(shí)時(shí)處理,結(jié)合大帶寬數(shù)據(jù)的快速壓縮和存儲(chǔ),是下一代高吞吐量衛(wèi)星服務(wù)所必需的。問題是如何找到一款合適的有足夠容量、速度和可靠性的宇航級(jí)大容量存儲(chǔ)器。

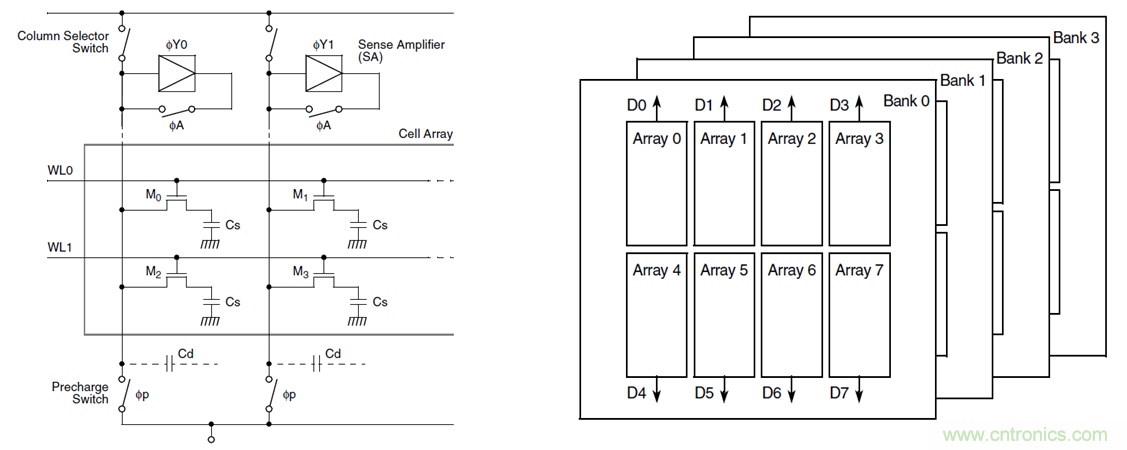

SDRAM是一種快速大容量的半導(dǎo)體技術(shù),它由單元的邏輯陣列和基本的存儲(chǔ)元件組成,每個(gè)存儲(chǔ)元件都包括一個(gè)電容和一個(gè)FET組成的控制門電路。每個(gè)單元存儲(chǔ)一個(gè)比特,下圖是一個(gè)簡(jiǎn)單的4比特存儲(chǔ)器。每一行的電壓控制晶體管的通斷,并對(duì)相關(guān)的電容充電或放電。在每個(gè)所需的“字線”充電之后,列選擇器選擇對(duì)應(yīng)的電容,準(zhǔn)備接下來的讀/寫操作。由于自放電效應(yīng),這些單元必須周期性刷新,包括讀和數(shù)據(jù)寫回的操作。

圖 2 : SDRAM位單元和SDRAM芯片的組織結(jié)構(gòu)

SDRAM架構(gòu)包含許多存儲(chǔ)單元,這些存儲(chǔ)單元組成行和列的二維陣列。要選擇某一個(gè)比特,需首先確定對(duì)應(yīng)的行,然后確定對(duì)應(yīng)的列。當(dāng)對(duì)應(yīng)的行開啟時(shí),可以訪問多個(gè)列,從而提高連續(xù)讀/寫的速度并降低延遲。

為了增加字容量,存儲(chǔ)器使用多個(gè)陣列,這樣當(dāng)需要進(jìn)行一次讀/寫操作時(shí),存儲(chǔ)器只需要尋址一次訪問每個(gè)陣列中的1個(gè)比特。

為了增加存儲(chǔ)器的整體容量,SDRAM的內(nèi)部結(jié)果還包含多個(gè)bank,如上圖所示。這些bank互相交織,進(jìn)一步提高了性能,并可以獨(dú)立尋址。

當(dāng)需要執(zhí)行讀或?qū)懖僮鲿r(shí),首先存儲(chǔ)器控制器發(fā)出ACTIVE命令,激活對(duì)應(yīng)的行和bank。操作執(zhí)行完畢后,PRECHARGE命令關(guān)閉一個(gè)或多個(gè)bank中的一個(gè)對(duì)應(yīng)的行。除非之前的行被關(guān)閉,否則無法打開新的行。

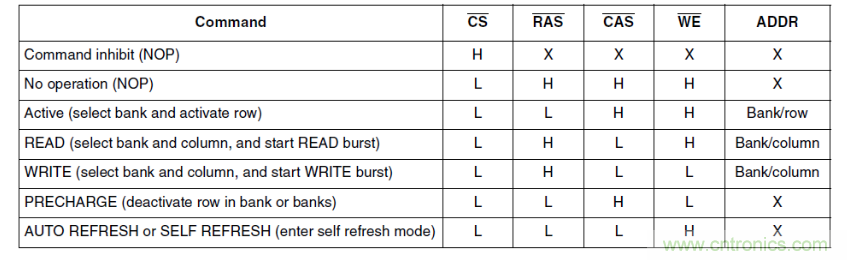

SDRAM的操作通過如下的控制信號(hào)實(shí)現(xiàn):片選(CS)、數(shù)據(jù)屏蔽(DQM)、寫使能(WE)、行地址選通(RAS)和列地址選通(CAS)。后面的三個(gè)信號(hào)決定發(fā)出哪個(gè)命令,如下表所示:

表 1 : SDRAM控制真值表

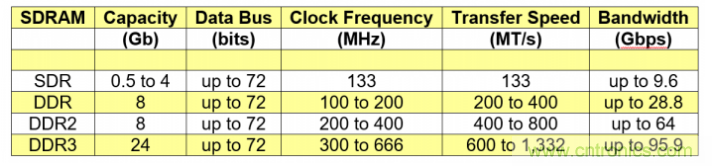

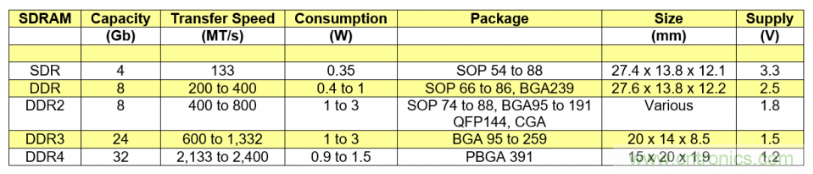

從1992年至今,SDRAM已發(fā)展了數(shù)代:最早的版本是單倍數(shù)據(jù)速率(SDR)型SDRAM,其內(nèi)部時(shí)鐘頻率和I/O速率相同。SDR型SDRAM一個(gè)時(shí)鐘周期只能讀或?qū)懸淮?,在開始下個(gè)操作之前必須等待當(dāng)前操作完成。

雙倍數(shù)據(jù)率(DDR)型SDRAM通過在兩個(gè)時(shí)鐘邊沿傳送數(shù)據(jù),在不提高時(shí)鐘頻率的情況下使I/O傳送的速度加倍,從而實(shí)現(xiàn)了更大的帶寬。這是采用一種2n預(yù)讀取的架構(gòu),其內(nèi)部數(shù)據(jù)路徑是外部總線寬度的兩倍,允許內(nèi)部頻率是外部傳送速度的一半。對(duì)于每個(gè)讀操作,可獲取2個(gè)外部字;而對(duì)于每個(gè)寫操作,兩個(gè)外部數(shù)據(jù)字在內(nèi)部合并,并在一個(gè)周期內(nèi)寫入。DDR1是一種真正的源同步設(shè)計(jì),通過使用雙向數(shù)據(jù)選通在一個(gè)時(shí)鐘周期捕捉兩次數(shù)據(jù)。

DDR2型SDRAM的外部總線速度是DDR1的雙倍I/O傳送速度的兩倍。它使用4n預(yù)讀取的緩沖,內(nèi)部的數(shù)據(jù)路徑是外部數(shù)據(jù)總線寬度的四倍。DDR2的時(shí)鐘頻率可設(shè)置成DDR1的一半,實(shí)現(xiàn)相同的傳送速度;或相同的速率,實(shí)現(xiàn)雙倍的信息帶寬。

DDR3型SDRAM的外部總線速度是DDR2雙倍I/O傳送速率的兩倍,使用8n預(yù)讀取架構(gòu)。它的內(nèi)部數(shù)據(jù)路徑的寬度是8比特,而DDR2是4比特。DDR3的時(shí)鐘頻率可設(shè)置成DDR2的一半,實(shí)現(xiàn)相同的傳輸速度;或相同的速率,實(shí)現(xiàn)雙倍的信息帶寬。

表2列出了當(dāng)前衛(wèi)星和航天器制造商可用的宇航級(jí)SDRAM的選項(xiàng)。

表 2 : 當(dāng)前的宇航SDRAM選項(xiàng)

為了實(shí)現(xiàn)下一代高吞吐量衛(wèi)星的服務(wù),未來的載荷需要更快、更大容量、更小尺寸和更低功耗的星載存儲(chǔ)器。小衛(wèi)星星座對(duì)尺寸和功耗有更嚴(yán)格的限制,而OEM廠商也需要更大的存儲(chǔ)帶寬實(shí)現(xiàn)實(shí)時(shí)應(yīng)用。

Teledyne-e2v最近發(fā)布了第一款面向宇航應(yīng)用的耐輻射DDR4 SDRAM。DDR4T04G72是一款72比特4GB(32Gb)的存儲(chǔ)器,目標(biāo)I/O速度2400MT/s,有效帶寬153.6 Gbps(帶ECC)或172.8 Gbps(不帶ECC)。器件的封裝是緊湊的15x20x1.92mm的PBGA,包含391個(gè)焊球,間距0.8mm,如下圖所示。這款器件可提供-55℃到+125℃和-40℃到+105℃兩種溫度范圍,其有鉛的版本經(jīng)過NASA Level 1和ESCC class 1的質(zhì)量認(rèn)證。將來也有計(jì)劃發(fā)布8GB(64Gb)的版本。

圖 3 : 耐輻射DDR4T04G72, 4 GB DDR4存儲(chǔ)器

對(duì)于防輻射性能,DDR4T04G72的SEL閾值超過60.8 MeV.cm2/mg,SEU和SEFI的閾值分別是8.19和2.6 MeV.cm2/mg,目標(biāo)100 krad(Si)TID免疫。

4GB DDR4T04G72是一款包含5個(gè)裸片的MCM,其中4個(gè)是1 GB(8 Gb)的存儲(chǔ)容量,512 Mb x 16 bits結(jié)構(gòu),分為兩個(gè)組,每個(gè)組有4個(gè)bank。為了提高可靠性,器件采用了72比特的數(shù)據(jù)總線,包含64比特的數(shù)據(jù)和8比特的錯(cuò)誤檢測(cè)與糾正。這個(gè)ECC功能是通過第五個(gè)裸片實(shí)現(xiàn)的。器件使用內(nèi)部的8n預(yù)讀取緩沖,實(shí)現(xiàn)高速操作,提供可編程的讀寫操作和額外的延遲。

DDR4的供電電壓的典型值是1.2V。下表是DDR4T04G72的物理尺寸和功耗與市面上的宇航級(jí)SDRAM的對(duì)比。功耗在很大程度上與下面幾個(gè)因素相關(guān):器件的架構(gòu)、時(shí)鐘頻率、供電電壓、執(zhí)行的操作、器件的狀態(tài)(如使能、預(yù)充電或讀/寫)、每個(gè)狀態(tài)的持續(xù)時(shí)間、是否使用bank交織和I/O電路的實(shí)現(xiàn)(如終端電路)。SDRAM在系統(tǒng)中的使用方式的不同,也會(huì)對(duì)功耗有很大的影響。對(duì)于系統(tǒng)設(shè)計(jì),非常重要的一點(diǎn)是,您需要考慮存儲(chǔ)器如何被訪問、如何被特定的PDN驅(qū)動(dòng)以及如何設(shè)計(jì)散熱方案。DDR4也支持2.5V的電壓Vpp,其為器件提供字線加速以提升效率。

表 3 : SDRAM的參數(shù)比較

您可以從Teledyne e2v獲取DDR4T04G72的IBIS、SPICE、熱模型和散熱估算表。若您想把這款器件配合Xilinx’s XQRKU060宇航級(jí)FPGA一起使用,Teledyne e2v可以提供使用Vivado® Design Suite生成DDR4控制器IP的配置文件供您參考。

您也可以選擇下圖這款小型單基板44x26mm的模塊,包含DDR4T04G72 DDR4 SDRAM和一款耐輻射四核64比特ARM® Cortex® A72 CPU,其工作頻率高達(dá)1.8 GHz。對(duì)于這款宇航級(jí)模塊,目前Teledyne e2v還未決定提供有鉛還是RoHS的封裝。

您更喜歡哪一款產(chǎn)品?請(qǐng)您把您的想法發(fā)郵件至thomas.porchez@teledyne.com。

圖 4 : 耐輻射QLS1046-4GB quad ARM core和DDR4T04G72 DDR4存儲(chǔ)器

DDR4將為宇航產(chǎn)業(yè)提供高吞吐量板上計(jì)算的方案,提高采集系統(tǒng)的性能,使諸如超高分辨率成像、流媒體視頻直播和星上人工智能等新一代地球觀測(cè)、宇航科學(xué)和電信應(yīng)用變?yōu)榭赡堋?/div>

DDR4T04G72使衛(wèi)星和航天器的制造商第一次可以使用大存儲(chǔ)帶寬技術(shù),而類似的技術(shù)在商業(yè)領(lǐng)域已經(jīng)使用了6年了。與市場(chǎng)上的經(jīng)過認(rèn)證的DDR3 SDRAM相比,DDR4T04G72可與最新的宇航級(jí)FPGA和微處理器配合使用,實(shí)現(xiàn):

● 存儲(chǔ)器帶寬增加62%,傳輸速度加倍

● 存儲(chǔ)容量增加25%

● 物理尺寸縮小76%

本文的作者是Spaceships公司的CEO和創(chuàng)始人Rajan Bedi博士。

推薦閱讀: