【導(dǎo)讀】SPI是一種非常有用且靈活的標(biāo)準(zhǔn),但它的靈活性來源于它的簡潔。四個單向中等速度隔離通道將處理時鐘速率為數(shù)MHz的SPI。而設(shè)計人員放棄的是諸如中斷服務(wù)支持等功能,以及諸如復(fù)位功能或從非SPI支持報警功能等直接通信通道。其結(jié)果是,頻繁使用SPI的接口具有并行工作的額外GPIO線路,以便處理這些功能。隔離SPI時,所有這些線路也都需要隔離。

很多情況下,額外通信不需要高速,因此設(shè)計人員便從認(rèn)證器件列表上選用幾個光耦合器,而不再使用SPI所需的高速數(shù)字隔離器。但是,光耦合器不如數(shù)字隔離器那么容易設(shè)計,尤其是簡單的低速光耦合器。設(shè)計師也許需要上一堂“光耦合器電流傳輸比(CTR)如何隨時間和溫度變化而變,以及它如何影響應(yīng)用速度”的速成課。如果多個方向需要額外的通信,那么就需要使用多個封裝,因為如果光耦合器是一個多通道器件,則其通道就必須沿同一個方向傳輸數(shù)據(jù)。隨著設(shè)計的逐步展開,尺寸、成本和時間投入便會快速增加。

使用基于iCoupler?數(shù)字隔離器的隔離SPI

使用四通道高速數(shù)字或光學(xué)隔離可輕松隔離SPI總線。四通道數(shù)字隔離器能以緊湊的尺寸實(shí)現(xiàn)隔離,且通常支持5 MHz至10 MHz SPI時鐘速率。無論基于集成式微變壓器、電容或光耦合器,都需要跨越隔離柵傳輸信號。在電流隔離技術(shù)中,有兩種主要的編碼方案可以耦合輸入信號:邊沿編碼和電平編碼。電平編碼方案允許采用傳播延遲較低的隔離器,并且一般而言空閑時的功耗更高,時序性能(抖動和PWM)較差。另一方面,邊沿編碼方案功耗較低,且時序性能較好。然而,很多基于邊沿的部署具有較長的傳播延遲,從而限制了SPI總線的時鐘速度。我們將探索消除這種限制以及實(shí)現(xiàn)極高性能SPI總線隔離的技巧。

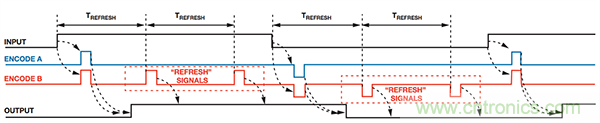

在邊沿編碼方案中,輸入數(shù)字轉(zhuǎn)換跨越隔離柵進(jìn)行編碼。然后,通過解碼這些轉(zhuǎn)換信號,在輸出端再現(xiàn)數(shù)字輸入。圖1中的示例波形(A類)顯示如何對輸入邊沿進(jìn)行差分編碼。上升和下降輸入轉(zhuǎn)換分別編碼為窄正脈沖和負(fù)脈沖。

只要數(shù)字輸入正在切換,信號就會正常傳輸,但如果發(fā)生輸入至輸出直流電平失配,則失配會一直存在,除非對其進(jìn)行校正。這在數(shù)據(jù)通道空閑時上電最為明顯;無信號跨越隔離柵進(jìn)行輸入引腳直流狀態(tài)通信,且邊沿傳輸前啟動狀態(tài)可能不匹配輸入數(shù)據(jù)。為了解決這個問題,邊沿編碼方案采用了某種形式的“刷新”電路,確保在輸出端進(jìn)行直流校正。在輸入靜止的預(yù)設(shè)時間(TREFRESH)之后,通過周期性跨越隔離柵傳輸最后一次轉(zhuǎn)換可實(shí)現(xiàn)刷新。圖1還顯示了示例邊沿編碼方案中的刷新(B類波形)。

圖1. 跨越隔離柵的編碼波形示例。A類和B類分別為帶與不帶刷新信號的編碼波形。

在該波形上,哪怕輸入信號未在上升沿和下降沿之間轉(zhuǎn)換,多個編碼上升轉(zhuǎn)換也會跨越隔離柵傳輸,以便刷新接收器狀態(tài)并確保接收器處于高電平狀態(tài)。顯然,除了確保上電時具有正確的輸出狀態(tài),刷新電路還有助于校正輸出狀態(tài)(若輸出遭破壞并與輸入狀態(tài)不同步)。由于編碼數(shù)據(jù)持續(xù)傳輸,該方案產(chǎn)生空閑功耗。由于在邊沿編碼方案中要求刷新,了解該方案固有的時序影響很重要。從圖1中的波形可知,輸入轉(zhuǎn)換和刷新信號均通過同樣的隔離通道傳輸,但時間獨(dú)立。輸入信號完全異步于內(nèi)部刷新生成電路,因而刷新上一次轉(zhuǎn)換傳輸?shù)耐瑫r可能發(fā)生輸入轉(zhuǎn)換。這可能會在接收器端損害時序,導(dǎo)致邏輯錯誤。為了避免這種時序沖突錯誤,會要求刷新電路的信號路徑增加一定的“預(yù)判”延遲。

該延遲可確??缭礁綦x柵的編碼信號之間具有最小隔離,從而允許接收器明確解碼一切編碼傳輸序列。缺點(diǎn)是隨著速度的增加,這種延遲會大幅增加隔離器的傳播延遲,進(jìn)而限制滿足SPI時序要求的能力。

幸運(yùn)的是,這種限制是可以解決的。如果輸入轉(zhuǎn)換和刷新狀態(tài)通過不同的隔離元件傳輸,并且隨后在輸出端匯合,則無需任何預(yù)判延遲,且伴隨著時序性能的下降。將此構(gòu)想擴(kuò)展至多通道隔離器,則所有通道的刷新狀態(tài)可在單個隔離通道內(nèi)時間多路復(fù)用,然后解復(fù)用并與相應(yīng)輸出合并?;旧?,輸入狀態(tài)經(jīng)采樣、封裝后,以串行方式跨越隔離柵傳輸。接收器持續(xù)跟蹤輸入直流狀態(tài),然后根據(jù)輸入保持非活動的時間決定使用直流狀態(tài)或是最后一次輸入轉(zhuǎn)換來更新輸出。由于僅有一個額外的數(shù)字隔離器通道搭載全部刷新狀態(tài),因此可以釋放所有輸入通道的預(yù)判延遲,并使其僅搭載輸入開關(guān)信息,從而大幅改善傳播延遲。圖2顯示了這一構(gòu)想。

圖2. 搭載輸入1和輸入2刷新時間多路復(fù)用的專用第三隔離通道功能框圖。

ADI SPIsolator?系列高速數(shù)字隔離器采用該方案實(shí)現(xiàn)SPI通道的極低傳播延遲,從而實(shí)現(xiàn)高達(dá)17 MHz的高帶寬隔離SPI總線部署。額外的隔離器通道搭載刷新信息,并通過將數(shù)據(jù)時間多路復(fù)用至跨越隔離柵來回傳輸?shù)臄?shù)據(jù)包中,實(shí)現(xiàn)傳輸各種其他低吞吐率信號的額外用途。這樣可以實(shí)現(xiàn)除SPI串行數(shù)據(jù)位以外的其他通信,從而獲得功能多樣化且高度集成的隔離式SPI總線。

帶輔助數(shù)據(jù)通道的SPI

SPIsolator產(chǎn)品系列中的部分型號在多路復(fù)用刷新通道上集成三個250 kbps輔助數(shù)字通道。三個不同的產(chǎn)品型號允許針對這些輔助通道進(jìn)行多通道方向配置。哪怕輔助通道異步,它們也會在通過單隔離通道傳輸前進(jìn)行采樣和數(shù)據(jù)包封裝。這些輔助通道的傳播延遲變化量最高可達(dá)2.6 μs,具體取決于通道輸入何時根據(jù)內(nèi)部采樣時鐘切換。對異步輔助信號進(jìn)行采樣和串行化還能將其與內(nèi)部采樣時鐘同步。如果慢信號之間具有精確的時序很重要,那么這可能導(dǎo)致時序問題,對于1.2 μs或更短時間窗口內(nèi)的精度而言更是如此。幸運(yùn)的是,典型SPI總線周圍僅有極少數(shù)輔助信號之間要求具備如此精確的時序關(guān)系。更為重要的是,該低速數(shù)據(jù)系統(tǒng)經(jīng)過仔細(xì)設(shè)計,可保留(多個異步通道的)邊沿階數(shù)——只要邊沿由至少一個最小偏斜隔離(VIXSKEW)。換言之,如果某個邊沿在輸入端超前另一個邊沿,則隔離器不會反轉(zhuǎn)階數(shù)。

通用SPI接口示例

圖3. 采用多種技術(shù)實(shí)現(xiàn)補(bǔ)充功能的典型SPI應(yīng)用。

圖3是一個典型SPI應(yīng)用,該應(yīng)用要求1 MHz SCLK、四線式SPI以及三個用于中斷、電源良好和復(fù)位的額外信號。低速通道可能僅需40 μs傳播延遲。選擇這些參數(shù),以便檢查所有元器件選項。時序處于所有主要類型隔離器的能力范圍內(nèi),因此可以獨(dú)立于性能之外比較解決方案尺寸與成本的集成效應(yīng)。以下提供部分實(shí)施選項:

1) 使用全部光耦合器

2) 針對慢信號通道的SPI和光耦合器使用數(shù)字隔離器

3) 使用全集成式數(shù)字隔離器,比如ADI SPIsolator

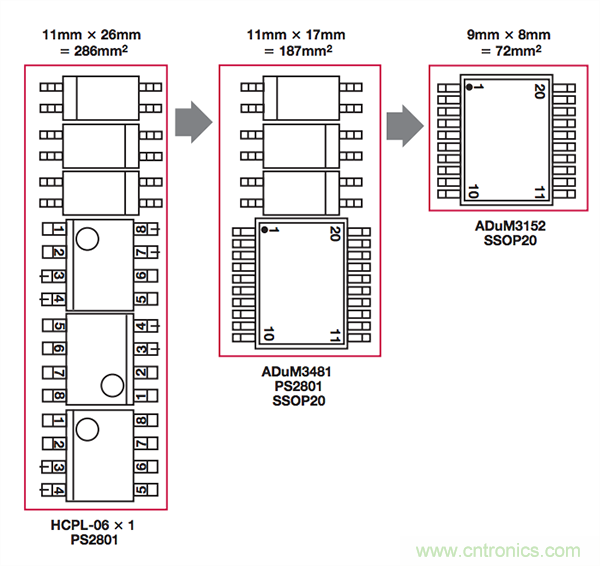

就原理圖而言,這些解決方案大致相似。然而,如果仔細(xì)看圖4的話,可以發(fā)現(xiàn)IC如何在PCB上布局。紅框大致框出了隔離元器件所需的范圍,以及允許放置無源器件的位置。

以混合速度光耦合器解決方案為基準(zhǔn),很多設(shè)計人員會試圖將標(biāo)準(zhǔn)數(shù)字隔離器與成本極低的光耦合器組合,并以為那就是性價比最高的低速信號采樣實(shí)現(xiàn)方法。解決方案之間很大一部分的差異是因為數(shù)字隔離器允許在單個封裝內(nèi)混合通道方向,避免了大量的封裝開銷。混合技術(shù)解決方案可能具有較高的性價比,但額外犧牲了設(shè)計時間,并產(chǎn)生穩(wěn)定性問題。廉價的光耦合器速度很慢,且由于結(jié)構(gòu)簡單而需要細(xì)研究考量才能成功完成設(shè)計。必須非常仔細(xì)確保它們隨時間和溫度變化的穩(wěn)定性,同時盡可能降低功耗。

從光耦合器解決方案轉(zhuǎn)為完全集成式解決方案(比如ADI ADuM3152 SPIsolator的集成式解決方案內(nèi)置通道間速度差和脈沖階數(shù)反轉(zhuǎn)保護(hù)功能,無設(shè)計開銷、無需占用額外的電路板空間。集成式解決方案的低速通道還支持遠(yuǎn)高于單個晶體管光耦合器的數(shù)據(jù)速率。集成式解決方案的成本遠(yuǎn)低于光耦合器解決方案的一半,并且相比分立式光耦合器每通道具有更低的低速通道成本??紤]到SPI性能,則ADuM3152數(shù)字隔離解決方案可支持高達(dá)17 MHz時鐘速率的SPI,因為其傳播延遲極短;而光耦合器的“快速”通道能以合理的成本在最高3 MHz頻率下工作。

圖4. 采用光耦合器實(shí)現(xiàn)補(bǔ)充功能的典型SPI應(yīng)用。

解復(fù)用SSB以控制多達(dá)4個從機(jī)

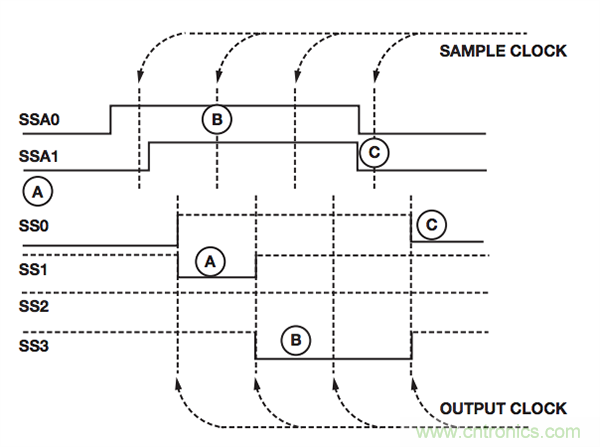

在ADuM3154產(chǎn)品的變體中,250 kbps、低速、雙通道地址總線用來控制隔離式從機(jī)選擇地址線(SSx),允許在最短2.6 μs時間內(nèi)改變目標(biāo)從機(jī)器件。圖6中的部署使用了通用隔離器和ADuM3154。圖5顯示了SSx如何跟隨地址位(SSAx)的改變而轉(zhuǎn)換。

ADuM3154使用2位地址總線將主機(jī)-從機(jī)選擇(MSS)路由至四個從機(jī)之一。這些地址總線位都是慢速信號,它們再次綁定四個常用高速SPI通道的刷新狀態(tài)。 就像刷新狀態(tài),地址位經(jīng)采樣、封包后,以串行方式跨越隔離柵傳輸。在從機(jī)側(cè)對數(shù)據(jù)包進(jìn)行去串行處理,地址位用來解復(fù)用MSS。解復(fù)用器將在2.6 μs內(nèi)將MSS信號路由至所需從機(jī),具體時間取決地址總線何時相對于內(nèi)部采樣時鐘進(jìn)行切換。地址位是總線的一部分,必須互相同步。采樣和串行化期間必須非常謹(jǐn)慎,以保證這些地址位在輸出側(cè)互相保持同步,尤其是從某個選定的從機(jī)轉(zhuǎn)換至另一個從機(jī)時。

圖5. 從機(jī)選擇地址位SSAx選擇四個從機(jī)之一(即SSx)。

多從機(jī)SPI接口示例

一個常見的SPI設(shè)計要求是與共享同一個SPI總線的多個從機(jī)器件對話。這可以通過多種方式實(shí)現(xiàn)。如果數(shù)據(jù)同時從所有次級端器件采樣而來,并且所有數(shù)據(jù)的每一幀都傳輸,則最簡單的方法是采用菊花鏈將器件連接起來,并將整個鏈路上的所有器件信號通過單個隔離端口順序移出。但如果數(shù)據(jù)采集序列不固定,則每一個SPI從機(jī)都必須單獨(dú)尋址。這就為隔離式接口提出了特定的挑戰(zhàn)。

如果每一個從機(jī)都必須獨(dú)立尋址,則每個器件都必須有獨(dú)立的從機(jī)選擇線。很多情況下,從機(jī)選擇不僅選擇特定目標(biāo)用于SPI通信,還會發(fā)起ADC轉(zhuǎn)換(舉例而言),因此該條線路還必須具有高度精確的時序性能。在很多部署中,這就要求提供額外的隔離通道,并具有與時鐘通道相當(dāng)?shù)乃俣龋员A魰r序。一

款四通道隔離SPI設(shè)計如圖6所示;圖中,標(biāo)準(zhǔn)四通道高速隔離采用三個額外的高速隔離通道予以加強(qiáng)。

從機(jī)選擇的另一種方法如圖6右半部分所示。在次級端使用一個多路復(fù)用器,而較低速度的隔離選擇線可用來選擇目標(biāo)。必須謹(jǐn)慎切換多路復(fù)用控制線,以防它們在時序略為失配時躍遷至不正確的中間狀態(tài)。該方案采用SPIsolator器件所提供的低速通道實(shí)現(xiàn),并且由于應(yīng)用定義良好,因此可以內(nèi)部構(gòu)建對于不確定狀態(tài)的保護(hù),防止小的時序誤差造成瞬時輸出狀態(tài)。

圖6. 典型多從機(jī)SPI應(yīng)用。

在最終分析中,若無論何種技術(shù)都能達(dá)到性能要求,則最佳設(shè)計選擇便出于容易部署、尺寸和成本考慮。圖7顯示了三種可能的部署,從左到右依次是:使用7個隔離通道的簡單光耦合器、使用數(shù)字隔離器的同一款方案、使用SPIsolator集成式多路復(fù)用器功能的方案。光耦合器解決方案尺寸最大,數(shù)字隔離器尺寸是前者的72%,而SPIsolator僅占PCB尺寸面積的36%。三個解決方案的成本對比也和面積類似,SPIsolator方案的成本相比其他方案大幅降低。

圖7. 采用光耦合器實(shí)現(xiàn)補(bǔ)充功能的典型SPI應(yīng)用。

結(jié)論

設(shè)計高性能隔離式SPI解決方案時,SPIsolator產(chǎn)品系列可以通過多路復(fù)用控制通道來支持高速SPI,其傳播延遲極低,且輔助功能的集成度極高。該SPI通道組合包含補(bǔ)充功能,具有方便的高度集成式隔離SPI總線設(shè)計,同時縮短設(shè)計時間,降低成本和電路板占位空間。

推薦閱讀: