【導(dǎo)讀】S逐次逼近型(SAR) ADC提供高分辨率、出色的精度和低功耗特性。一旦選定一款精密SAR ADC,系統(tǒng)設(shè)計師就必須確定獲得最佳結(jié)果所需的支持電路。需要考慮的三個主要方面是:模擬輸入信號與ADC接口的前端、基準電壓源和數(shù)字接口 。本文將重點介紹前端設(shè)計的電路要求和權(quán)衡因素。關(guān)于其它方面的有用信息,包括具體器件和系統(tǒng)信息,請參閱數(shù)據(jù)手冊和本文的 參考文獻.

前端包括兩個部分:驅(qū)動放大器和RC濾波器。放大器調(diào)節(jié)輸入信號,同時充當信號源與ADC輸入端之間的低阻抗緩沖器。RC濾波器限制到達ADC輸入端的帶外噪聲,幫助衰減ADC輸入端中開關(guān)電容的反沖影響。

為SAR ADC選擇合適的放大器和RC濾波器可能很困難,特別是當應(yīng)用不同于ADC數(shù)據(jù)手冊的常規(guī)用途時。根據(jù)各種影響放大器和RC選擇的應(yīng)用因素,我們提供了設(shè)計指南,可實現(xiàn)最佳解決方案。主要考慮因素包括:輸入頻率, 吞吐速率和 輸入復(fù)用.

選擇合適的RC濾波器

要選擇合適的RC濾波器,必須計算單通道或多路復(fù)用應(yīng)用的RC帶寬,然后選擇R和C的值。

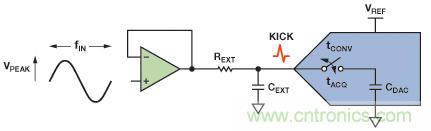

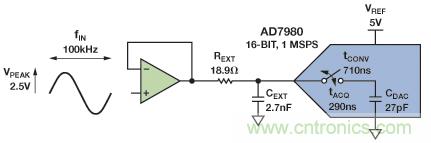

圖1顯示了一個典型的放大器、單極點RC濾波器和ADC。ADC輸入構(gòu)成驅(qū)動電路的開關(guān)電容負載。其10 MHz輸入帶寬意味著需要在寬帶寬內(nèi)保證低噪聲以獲得良好的信噪比(SNR)。RC網(wǎng)絡(luò)限制輸入信號的帶寬,并降低放大器和上游電路饋入ADC的噪聲量。不過,帶寬限制過多會延長建立時間并使輸入信號失真。

圖1. 典型放大器、RC濾波器和ADC

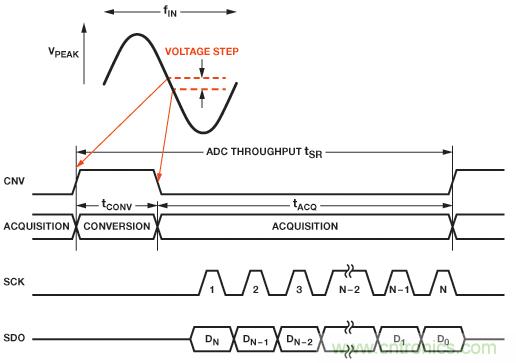

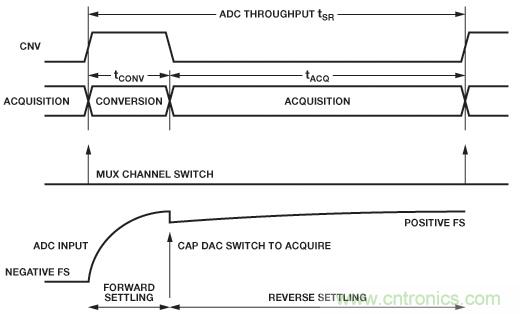

在建立ADC輸入和通過優(yōu)化帶寬限制噪聲時所需的最小RC值,可以由假設(shè)通過指數(shù)方式建立階躍輸入來計算。要計算階躍大小,需要知道輸入信號頻率、幅度和ADC轉(zhuǎn)換時間。轉(zhuǎn)換時間, tCONV(圖2)是指容性DAC從輸入端斷開并執(zhí)行位判斷以產(chǎn)生數(shù)字代碼所需的時間。轉(zhuǎn)換時間結(jié)束時,保存前一樣本電荷的容性DAC切換回輸入端。此階躍變化代表輸入信號在這段時間的變化量。此階躍建立所需的時間稱為 "反向建立時間".

圖2. N位ADC的典型時序圖

在給定輸入頻率下,一個正弦波信號的最大不失真變化率可通過下式計算:

如果ADC的轉(zhuǎn)換速率大大超出最大輸入頻率,則轉(zhuǎn)換期間輸入電壓的最大變化量為:

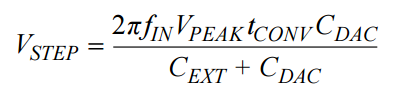

這是容性DAC切換回采集模式時出現(xiàn)的最大電壓階躍。然后,DAC電容與外部電容的并聯(lián)組合會衰減此階躍。因此,外部電容必須相對較大,達到幾nF。此分析假設(shè)輸入開關(guān)導(dǎo)通電阻的影響可忽略不計。現(xiàn)在需要建立的階躍大小為:

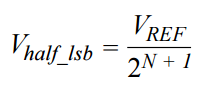

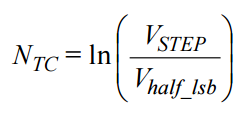

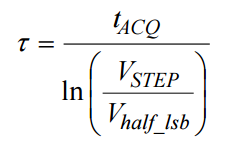

接下來計算在ADC采集階段,ADC輸入建立至½ LSB的時間常數(shù)。假設(shè)階躍輸入以指數(shù)方式建立,則所需RC時間常數(shù)τ為:

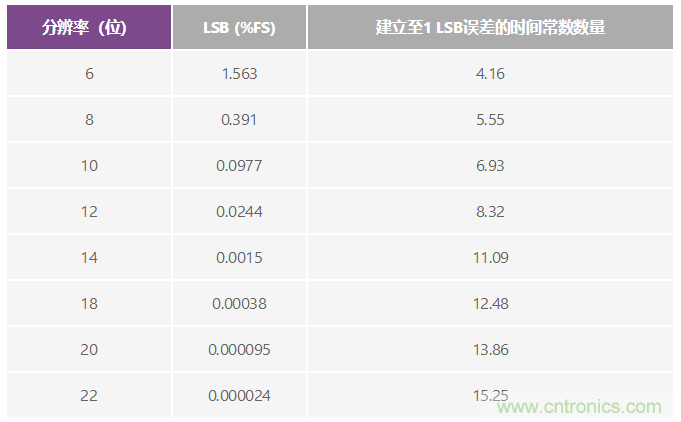

其中,tACQ 為采集時間,NTC 為建立所需的時間常數(shù)數(shù)目。所需的時間常數(shù)數(shù)目可以通過計算階躍大小VSTEP與建立誤差(本例為½ LSB)之比的自然對數(shù)來獲得:

因此,

將上式代入前面的公式可得:

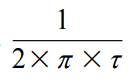

等效RC帶寬

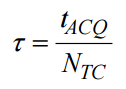

示例:借助RC帶寬計算公式,選擇16位ADCAD7980 (如圖3所示),其轉(zhuǎn)換時間為710 ns,吞吐速率為1 MSPS,采用5 V基準電壓。最大目標輸入頻率為100 kHz。計算此頻率時的最大階躍:

然后,外部電容的電荷會衰減此階躍。使用27 pF的DAC電容并假設(shè)外部電容為2.7 nF,則衰減系數(shù)約為101。將這些值代入VSTEP計算公式:

接下來計算建立至½ LSB(16位、5 V基準電壓)的時間常數(shù)數(shù)目:

采集時間為:

計算τ:

因此,帶寬為3.11 MHz, REXT 為 18.9 ?.

圖3. 采用16位1 MSPS ADC AD7980的RC濾波器

最小帶寬、吞吐速率和輸入頻率之間的這種關(guān)系說明:輸入頻率越高,則要求RC帶寬越高。同樣,吞吐速率越高,則采集時間越短,從而提高RC帶寬。采集時間對所需帶寬的影響最大;如果采集時間加倍(降低吞吐速率),所需帶寬將減半。此簡化分析未包括二階電荷反沖效應(yīng),它在低頻時變成主要影響因素。輸入頻率非常低時(<10 kHz,包括DC),容性DAC上建立的始終是大約100 mV的電壓階躍。此數(shù)值應(yīng)作為上述分析的最小電壓階躍。

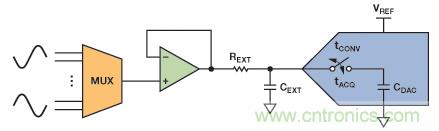

多路復(fù)用 輸入信號很少是連續(xù)的,通常由不同通道切換產(chǎn)生的大階躍組成。最差情況下,一個通道處于負滿量程,而下一個通道則處于正滿量程(見圖4)。這種情況下,當多路復(fù)用器切換通道時,階躍大小將是ADC的滿量程,對于上例而言是5 V。

圖4. 多路復(fù)用設(shè)置

在上例中使用多路復(fù)用輸入時,線性響應(yīng)所需的濾波器帶寬將提高到3.93 MHz(此時階躍大小為5 V,而非單通道時的1.115 V)。假設(shè)條件如下:多路復(fù)用器在轉(zhuǎn)換開始后不久即切換(圖5),放大器和RC正向建立時間足以使輸入電容在采集開始前穩(wěn)定下來。

圖5. 多路復(fù)用時序

對于計算得到的RC帶寬,可以利用表1進行檢查。從表中可知,要使?jié)M量程階躍建立至16位,需要11個時間常數(shù)(如表1)。對于計算的RC,濾波器的正向建立時間為11 × 40.49 ns = 445 ns,遠少于轉(zhuǎn)換時間710 ns。正向建立不需要全部發(fā)生在轉(zhuǎn)換期間(容性DAC切換到輸入端之前),但正向和反向建立時間之和不應(yīng)超過所需的吞吐速率。對于低頻輸入,信號的變化率低得多,因此正向建立并不十分重要。

表1. 建立至N位分辨率所需的時間常數(shù)數(shù)目

計算出濾波器近似帶寬后,就可以分別選擇REXT 和 CEXT 的值。上述計算假設(shè) CEXT = 2.7 nF,這是數(shù)據(jù)手冊所示應(yīng)用電路的典型值。如果選擇較大的電容,則當容性DAC切換回輸入端時,對反沖的衰減幅度會更大。然而,電容越大,驅(qū)動放大器就越有可能變得不穩(wěn)定,特別是給定帶寬下REXT 值較小時。如果 REXT 值太小,放大器相位裕量會降低,可能導(dǎo)致放大器輸出發(fā)生響鈴振蕩或變得不穩(wěn)定。對于串聯(lián) REXT較小的負載,應(yīng)采用低輸出阻抗的放大器來驅(qū)動??梢岳肦C組合和放大器的波特圖執(zhí)行穩(wěn)定性分析,以便驗證相位裕量是否充足。最好選擇1 nF至3 nF的電容值和合理的電阻值,以使驅(qū)動放大器保持穩(wěn)定。此外務(wù)必使用低電壓系數(shù)的電容,如NP0型,以保持低失真。

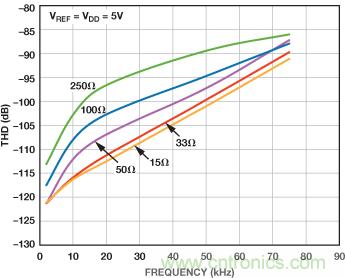

REXT的值必須能使失真水平保持在要求的范圍以內(nèi)。圖6顯示了驅(qū)動電路電阻對失真的影響與AD7690輸入頻率的函數(shù)關(guān)系。失真隨著輸入頻率和源電阻的提高而提高。導(dǎo)致這種失真的原因主要是容性DAC提供的阻抗的非線性特性。

圖6. 源電阻對THD的影響與輸入頻率的關(guān)系

低輸入頻率(<10 kHz)可以支持較大的串聯(lián)電阻值。失真還與輸入信號幅度有關(guān);對于同一失真水平,較低的幅度可以支持較高的電阻值。計算上例中的 REXT in the example above, where τ = 51.16 ns 假設(shè)CEXT 為2.7 nF,得到電阻值為18.9 Ω。這些值接近ADI數(shù)據(jù)手冊應(yīng)用部分給出的常見值。

此處計算的標稱RC值是有用的指南,但不是最終解決方案。選擇REXT與 CEXT之間的適當平衡點,需要了解輸入頻率范圍、放大器可以驅(qū)動多大的電容以及可接受的失真水平。為了優(yōu)化RC值,必須利用實際的硬件進行試驗,從而實現(xiàn)最佳性能。

選擇合適的放大器

在上一部分中,我們根據(jù)輸入信號和ADC吞吐速率,計算了適合ADC輸入的RC帶寬。接下來必須利用此信息選擇合適的ADC驅(qū)動放大器。需要考慮如下方面:

● 放大器大小信號帶寬

● 建立時間

● 放大器噪聲特性以及對系統(tǒng)噪聲的影響

● 失真

● 失真對于電源軌的裕量要求

該數(shù)據(jù)手冊通常會給出放大器的小信號帶寬 。但是,根據(jù)輸入信號的類型,大信號帶寬 可能更重要,尤其是高輸入頻率(>100 kHz)或多路復(fù)用應(yīng)用(因為電壓擺幅較大),而且輸入信號的正向建立更加關(guān)鍵。例如,ADA4841-1 的小信號帶寬為80 MHz(20 mV p-p信號),但大信號帶寬僅3 MHz(2 V p-p信號)。上例采用AD7980,計算的RC帶寬為3.11 MHz。對于較低的輸入頻率,ADA4841-1是很好的選擇,因為其80 MHz小信號帶寬對于反向建立而言綽綽有余,但在多路復(fù)用應(yīng)用中則有困難,因為對于大信號擺幅,此時的RC帶寬要求提高到3.93 MHz。這種情況下,更合適的放大器是ADA4897-1,它具有30 MHz的大信號帶寬。一般而言,放大器的小/大信號帶寬至少應(yīng)比RC帶寬大兩三倍,具體取決于是以反向建立還是正向建立為主。如果要求放大器級提供電壓增益(這會降低可用帶寬),更適用這條原則,甚至可能需要帶寬更寬的放大器。

看待正向建立要求的另一種方式是查看放大器的建立時間特性,它通常是指建立到額定階躍大小某一百分比所需的時間。對于16位到18位性能,通常要求建立到0.001%,但大多數(shù)放大器僅指定不同階躍大小的0.1%或0.01%建立時間。因此,為了確定建立特性是否支持ADC吞吐速率,需要對這些數(shù)值進行折中。ADA4841-1針對8 V階躍給出的0.01%建立時間為1 μs。在驅(qū)動1 MSPS(1 μs周期)AD7980的多路復(fù)用應(yīng)用中,它將無法使?jié)M量程階躍的輸入及時建立,但如果降低吞吐速率,例如500 kSPS可能是可行的。

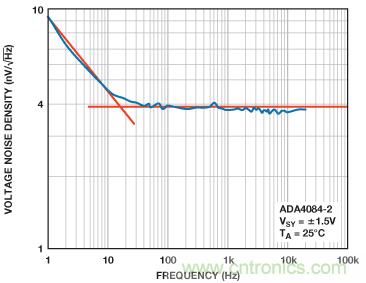

RC帶寬對于確定放大器的最大容許噪聲量十分重要。放大器噪聲一般通過低頻1/f噪聲(0.1 Hz至10 Hz)和高頻時的寬帶噪聲譜密度(圖7所示噪聲曲線的平坦部分)來規(guī)定。

圖7. ADA4084-2電壓噪聲與頻率的關(guān)系

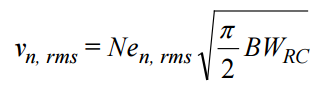

折合到ADC輸入端的總噪聲可以按照如下方法計算。首先,計算放大器寬帶頻譜密度在RC帶寬上的噪聲。

其中,en = 噪聲頻譜密度(V/√?Hz), N = 放大器電路噪聲增益,BWRC = RC 帶寬 Hz.

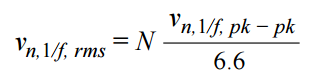

然后,通常通過下式計算低頻1/f噪聲;它通常指定為峰峰值,需要轉(zhuǎn)換為均方根值。

其中,

= 1/f峰峰值噪聲電壓,N = 放大器電路噪聲增益。

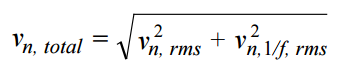

總噪聲為以上兩個噪聲的和方根:

為將驅(qū)動器噪聲對總SNR的影響降至最低,此總噪聲應(yīng)為ADC噪聲的1⁄10左右。根據(jù)目標系統(tǒng)的SNR要求,可能還允許更高的噪聲。例如,如果ADC的SNR為91 dB, VREF = 5 V,則總噪聲應(yīng)小于或等于

由此值很容易算出1/f噪聲和寬帶噪聲譜密度的最大允許值。假設(shè)擬用的放大器具有可忽略不計的1/f噪聲,以單位增益工作,并采用RC帶寬為上例計算值(3.11 MHz)的濾波器,那么

因此,該放大器的寬帶噪聲譜密度必須小于或等于2.26 nV/√?Hz。ADA4841-1的寬帶噪聲譜密度為2.1 nV/√?Hz,符合這一要求。

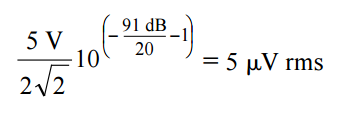

放大器需要考慮的另一個重要特性是特定輸入頻率時的失真。通常,為獲得最佳性能,16位ADC需要大約100 dB的總諧波失真(THD),18位ADC需要大約110 dB。圖8顯示對于2 V p-p輸入信號,ADA4841-1的典型失真與頻率的關(guān)系圖。

圖8. ADA4841-1的失真與頻率的關(guān)系

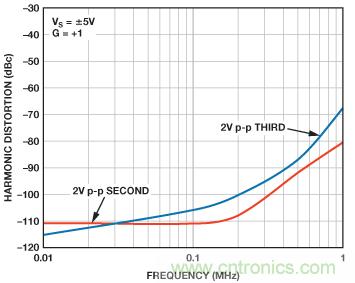

圖中顯示的不是總諧波失真,而是一般最為重要的二次和三次諧波成分。ADA4841-1的噪聲非常小,失真特性優(yōu)異,足以驅(qū)動18位ADC到大約30 kHz。當輸入頻率接近100 kHz或更高時,失真性能開始下降。為在高頻時實現(xiàn)低失真,需要使用功耗更高、帶寬更寬的放大器。較大的信號也會降低性能。對于0 V至5 V的ADC輸入,失真性能信號范圍將提高到5 V p-p。從圖8所示的失真圖可看出,這將產(chǎn)生不同的性能,因此放大器可能需要測試,以確保它滿足要求。圖9比較了多個輸出電壓水平的失真性能。

圖9. 不同輸出電壓水平下失真與頻率的關(guān)系

裕量,即放大器最大實際輸入/輸出擺幅與正負電軌之差,也可能影響THD。放大器可能具有軌到軌輸入和/或輸出,或者要求最高1 V甚至更大的裕量。即便是軌到軌輸入/輸出,如果工作信號電平接近放大器的供電軌,也將難以獲得良好的失真性能。因此,最好應(yīng)選擇讓最大輸入/輸出信號遠離供電軌的電源電平??紤]一個0 V至5 V輸入范圍的ADC,采用ADA4841-1放大器驅(qū)動,需要將ADC的范圍提高到最大。該放大器具有軌到軌輸出,對輸入有1 V的裕量要求。如果用作單位增益放大器,則至少需要1 V的輸入裕量,正電源至少必須是6 V。輸出為軌到軌,但仍然只能驅(qū)動到地或正供電軌的大約25 mV范圍內(nèi),因而需要一個負供電軌,以便一直驅(qū)動到地。為了給失真性能留有一定的裕量,負供電軌可以是–1 V。

如果允許降低ADC輸入范圍,從而喪失一定的SNR,則可以消除負電源。例如,如果ADC的輸入范圍降為0.5 V至5 V,此10%損失將導(dǎo)致SNR降低大約1 dB。然而,這樣就可以將負供電軌接地,從而消除用以產(chǎn)生負電源的電路,降低功耗和成本。

因此,選擇放大器時,務(wù)必考慮輸入和輸出信號范圍要求,以便確定所需的電源電壓。本例中,額定工作電壓為5 V的放大器不能滿足要求;但ADA4841-1的額定電壓高達12 V,所以使用較高的電源電壓將能實現(xiàn)出色的性能,并提供充足的電源裕量。

關(guān)于特殊器件的附加信息

具有軌到軌輸出的低功耗、低噪聲、低失真運算放大器

ADA4841-1低功耗運算放大器提供 2-nV/√?Hz 寬帶噪聲和–110 dBc無雜散動態(tài)范圍(SFDR),非常適合驅(qū)動16位和18位PulSAR® ADC,適用于便攜式儀器儀表、工業(yè)過程控制和醫(yī)療設(shè)備。該單位增益穩(wěn)定型放大器的特性包括:60 μV輸入失調(diào)電壓、114 dB開環(huán)增益、114 dB共模抑制、80 MHz帶寬(–3 dB)、12 V/µs壓擺率和175 ns的0.1%建立時間。輸入信號范圍可擴展至負供電軌以下100 mV,輸出擺幅可以達到任一供電軌的100 mV范圍內(nèi),從而提供單電源工作能力。ADA4841-1可采用2.7 V至12 V單電源或±1.5 V至±6 V雙電源供電,正常模式下的功耗為1.1 mA,掉電 模式下為40 μA。它采用8引腳SOIC封裝,額定溫度范圍為–40°C至+125°C,千片訂量報價為1.59美元/片。

具有軌到軌輸出的低噪聲、低功耗運算放大器

ADA4897-1是一款低噪聲、高速運算放大器,具有軌到軌輸出、1 nV/√?Hz 電壓噪聲、 2.8-pA/√?Hz 電流噪聲、230 MHz帶寬、120 V/µs壓擺率、45 ns建立時間,以及單位增益穩(wěn)定性,是超聲、低噪聲前置放大器,以及驅(qū)動高性能ADC和緩沖高性能DAC等應(yīng)用的理想選擇。AD4897-1采用3 V至10 V單電源供電,功耗為3 mA。它采用8引腳MSOP、LFCSP和SOIC封裝,額定溫度范圍為−40°C至+125°C,千片訂量報價為1.89美元/片。

功耗7 mW的16位、1 MSPS逐次逼近型ADC

AD7980低功耗逐次逼近型ADC提供16位分辨率,無失碼,采樣速率為1 MSPS。它接受0至VREF 范圍內(nèi)的偽差分輸入,特性包括91.5 dB信納比(SINAD)、–110 dB總諧波失真(THD)和最大±1.25 LSB積分非線性。逐次逼近架構(gòu)可確保無流水線延遲,菊花鏈配置則允許多個ADC共用一條總線。兩次轉(zhuǎn)換的間隙會自動掉電,其功耗與吞吐速率成正比。AD7980采用2.5 V單電源供電,1 MSPS時功耗為7 mW,10 kSPS時為70 μW,待機模式下為350 pA。它采用10引腳MSOP封裝,額定溫度范圍為–40°C至+85°C,千片訂量報價為11.95美元/片。

參考電路

AN-931 Application Note. Understanding PulSAR ADC Support Circuitry.

AN-1024 Application Note. How to Calculate the Settling Time and Sampling Rate of a Multiplexer.

MT-048 Tutorial. Op Amp Noise Relationships; 1/f Noise, RMS Noise, and Equivalent Noise Bandwidth.

Ardizzoni, John, Driving Miss ADC. RAQ-84, July 2012.

Ardizzoni, John. Great Expectations Come From Basic Understandings, RAQ-85, August 2012.

Ardizzoni, John, and Jonathan Pearson. “Rules of the Road” for High-Speed Differential ADC Drivers. Analog Dialogue, Volume 43, Number 2, 2009.

推薦閱讀: