【導讀】以LDMOS(橫向擴散金屬氧化物半導體)為代表的射頻大功率器件已經(jīng)在民用通信市場以其優(yōu)異的性能和低廉的價格而得到越來越廣泛的應用,對于這種射頻大功率器件的器件水平和能力評估也越來越受到關注。

本文基于負載牽引系統(tǒng),采用簡單、便捷以及可重復使用的理念,使用常規(guī)的微帶線階梯型阻抗變換器電路為基礎,充分考慮在應用測試中的偏置電路,進行前期使用ADS(Advanced Design System)仿真加后期驗證,設計制造了低耗無串擾的TRL(Though Reflected Delay)校準件,為測試得到射頻大功率器件的射頻性能奠定了優(yōu)異的基礎。

隨著通信的日益發(fā)展以及半導體功率器件研究和生產(chǎn)技術的突飛猛進,上世紀90年代末以前主要以硅雙極型晶體管和砷化鎵場效應管為核心的射頻微波功率放大器正被增益、線性度和輸出功率等方面更加優(yōu)秀的產(chǎn)品所取代(硅基射頻LDMOS以及氮化鎵場效應管)。這同時也對這些新技術、新產(chǎn)品的性能評估提出了更高的要求。目前國內(nèi)以945-960 MHz頻段的RF LDMOS功率管產(chǎn)品(單裸管芯輸出功率達到180瓦,線性增益達到19dB,效率達到70%,電壓駐波比達到10:1)已經(jīng)達到了實業(yè)化的目標。較之于傳統(tǒng)上常用的SOLT校準(適用于同軸校準),TRL校準對于在非同軸環(huán)境下進行射頻大功率器件的測試來說是一種非常精確的校準方式。這種校準方法的優(yōu)點在于其校準準確度只依賴于傳輸線的特征阻抗而不是其他標準,反射標準的反射系數(shù)和傳輸系數(shù)的長度都可以在校準中由計算得出,很好地避免了一些測試板引入的誤差,更能準確地反映被測器件的性能。

TRL校準件的要求

基于目前通用的射頻測試板材,我們選用4350B型板材,這種板材制造標稱的介電常數(shù)εr = 3.48,損耗因子為0.0037,板材厚度選取30mil,走線銅厚選取17μm。此次需要完成的目標頻段是2.0GHz~2.5GHz,制作出來的Reflect、Though以及Delay校準件均能滿足在此頻段內(nèi)反射系數(shù)Г(S11)<-10dB,傳輸系數(shù)T(S22)<-0.9dB。器件根部原始設計阻抗根據(jù)經(jīng)驗設定為2.5Ω,測試電路輸入輸出端口設計阻抗為通信系統(tǒng)設備通用的50Ω,端口采用常用的SMA型端子作為射頻信號輸入輸出的物理接口。

TRL校準件的構建

因為最終目的是為基于Load-Pull系統(tǒng)的器件做阻抗提取和性能評估,對于校準件的版圖設計基本需考慮通用性和成本,即在射頻信號主路采用微帶線階梯型阻抗變換器的基礎上,還需要在設計過程中考慮器件應用時所需要的直流偏置電路。

Part 1 射頻信號主路設計

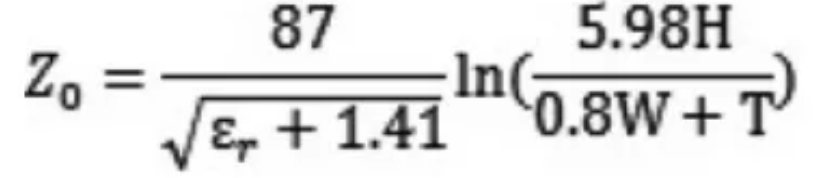

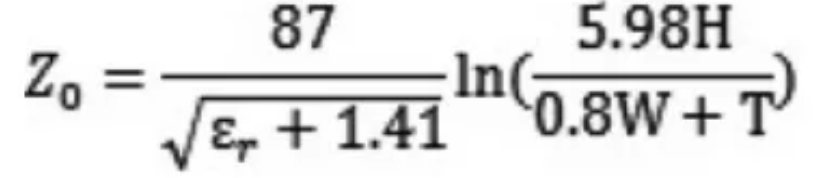

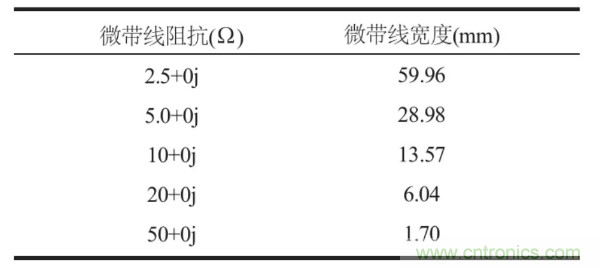

1、射頻信號主路設計由于從器件根部的2.5Ω變換到測試電路輸入輸出端口的50Ω,而且需要實現(xiàn)2.0GHz~2.5GHz的頻段跨越,為了確保在寬頻帶上能獲得良好的匹配性能,因此設計階梯為4級,對應設計的中間變換阻抗為:5Ω、10Ω、20Ω??梢圆捎孟旅娴淖杩褂嬎愎接嬎悖?/div>

其中,W為線寬,T為銅線厚度,εr為板材的介電常數(shù)。

在此我們運用Linecalc這個小軟件來計算和確定微帶線寬度,如圖1所示。

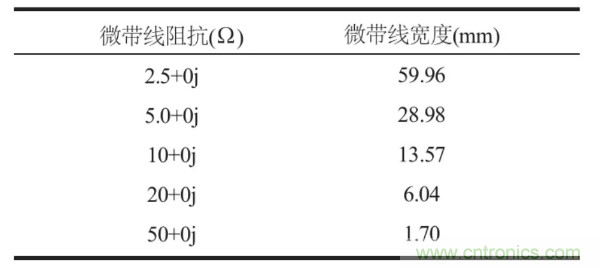

通過軟件計算得出微帶線寬度與設定阻抗的關系如表1:

圖1:ADS微帶線計算工具

表1:ADS微帶線計算結果

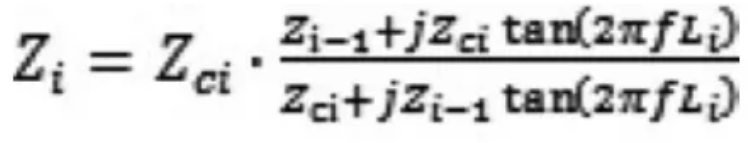

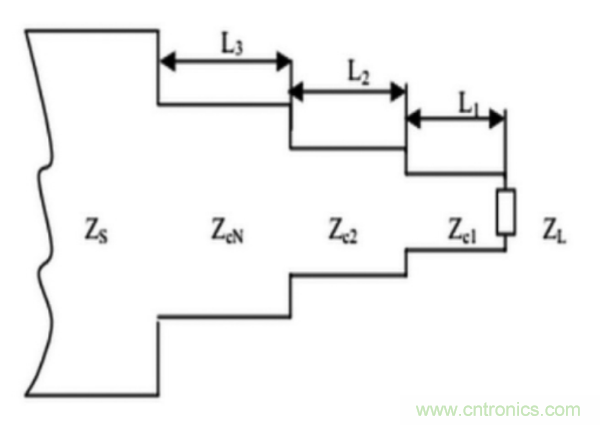

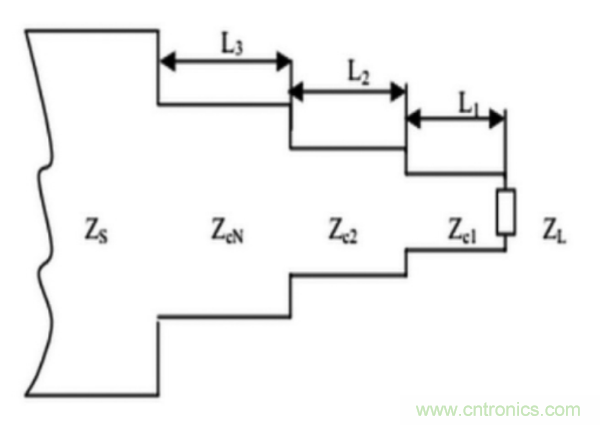

2、射頻信號主路設計的微帶線長度的設計思路為使用不定長度傳輸微帶線多階梯阻抗變換器(圖2)。根據(jù)傳輸線理論:第i節(jié)的輸入阻抗公式為:

這樣就可以使用遞推法計算出每一節(jié)微帶線的長度。在此由于考慮整個校準件是一個整體,以及還存在去除偏置電路的影響以及整個校準件不宜做得太大的問題,因此對于每一節(jié)微帶線的長度,我們將使用ADS的S-parameter調(diào)諧仿真,以及Layout之后的Momentum仿真,從整體上對微帶線的長度和寬度進行調(diào)節(jié),以達到能實現(xiàn)設計目標的要求。

圖2:階梯阻抗變換器

Part 2 直流偏置電路

直流偏置電路為射頻功率放大器主路的元器件提供一個工作狀態(tài),其設計的好壞將影響放大器的性能,尤其是漏極偏置電路的設計。一般直流偏置電路設計需要遵循的三個原則:

(1)偏置電路對信號主路影響要盡量的小,即不引入較明顯的附加耗損、反射以及高頻信號沿偏壓電路的泄露。

(2)為了偏置電路存在的大電流,需要考慮合理的偏置線寬度。

(3)盡量結構緊湊,簡單。

基于直流偏置電路的三個原則,我們選擇四分之一扇形開路線(即四分之一波長開路短截線的變形),這樣能夠很好滿足三原則的要求。扇形微帶短截線電抗可以由下列關系式出[5]:

在公式(3) 中,Ji(x)和Ni(x)是第一類和第二類貝塞爾函數(shù),α扇形微帶短截線的角度,εre是等效介質(zhì)常數(shù),λ0為自由空間波長,r1和r2是扇形微帶線的內(nèi)、外半徑,hW分別是介質(zhì)基片的厚度和微帶寬度,We是扇形短截線等效為微帶線的寬度。

根據(jù)設計的三原則,偏置線寬度的設計,尤其是器件漏端的偏置線線寬的設計,需要我們考慮電流承載能力,同時也需要考慮的是直流偏置銅線必須為盡量細的高阻線,因為這樣能減少偏置電路對于主路的影響。那么根據(jù)表2中銅箔寬度與承載電流的關系,我們就可以進行選擇。在此設計中我們考慮電流承受能力在1.2A左右,所以使用0.762的線寬也將電流承載能力的余量考慮在我們的設計中。

表2:銅箔寬度與承載電流的關系

TRL校準件的仿真與驗證

Part 1 校準件的仿真

通過上述對于整個TRL校準件的設計考慮,使用ADS工具,我們得到了本次根據(jù)仿真電路得出的可用于實際制作的PCB版圖,以及使用ADS的Momentum仿真出來的結果。

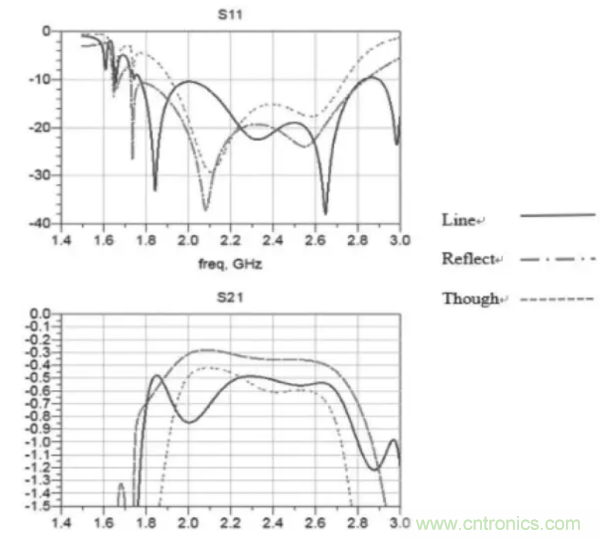

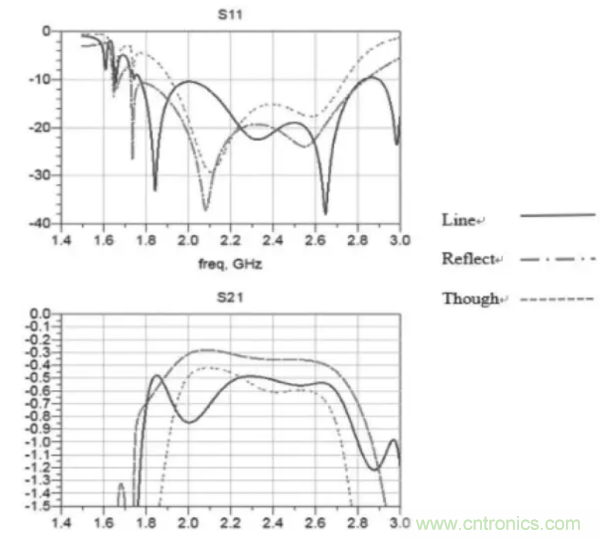

圖3中的S11和S21各有三條線段,分別代入Though、Reflect、Delay三塊校準件的反射系數(shù)和傳輸系數(shù)??疾?.0GHz、2.25GHz和2.5GHz三個典型頻點的值,在S11的曲線圖上,除Delay在2.0GHz點上只達到了-11dB,其余均低于-15dB;同樣在S21的曲線圖上,除Delay在2.0GHz點上接近于-0.9dB,其余均高于-0.7dB。應該說2.0GHz~2.5GHz這個頻段內(nèi)很好的達到了設計目標。

圖3:TRL校準件Momentum仿真圖

ADS這個軟件在仿真、優(yōu)化過程中有著優(yōu)異的性能,對于比較高要求和挑戰(zhàn)的性能指標能夠做好預先仿真,并實現(xiàn)PCB版圖電路,減少了工程反復和硬件材料的浪費,降低了設計成本,是一個很好的射頻工程應用工具。

Part 2 校準件的驗證

校準件的驗證分兩步進行,第一步是對校準件直接進行小信號測試驗證,第二步是使用頻率在 2.0GHz~2.5GHz之間的器件,在配合Load-Pull系統(tǒng)找到器件封裝根部阻抗后,再通過普通射頻電路測試板的匹配來驗證校準件是否符合設計要求。

1、校準件小信號參數(shù)的驗證

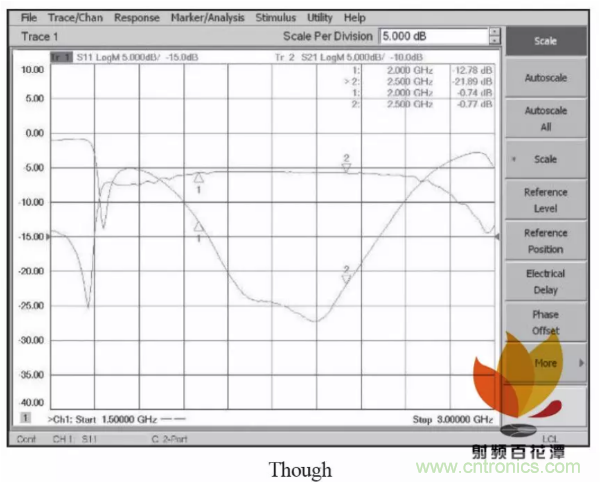

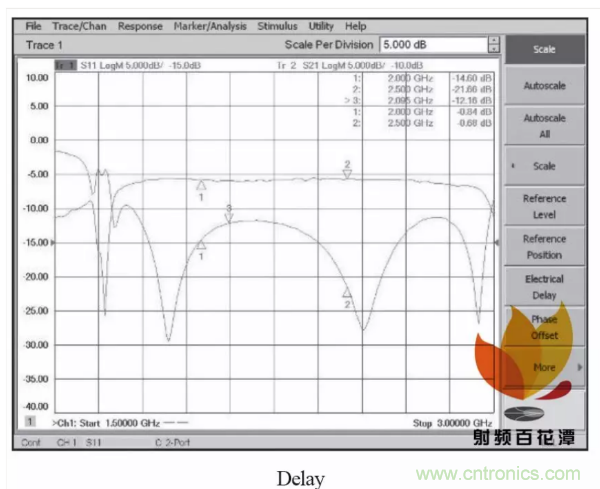

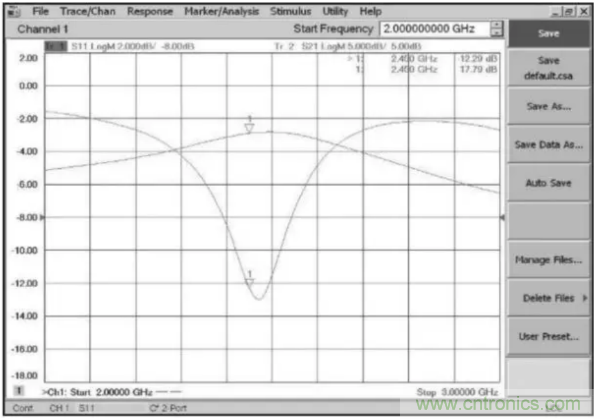

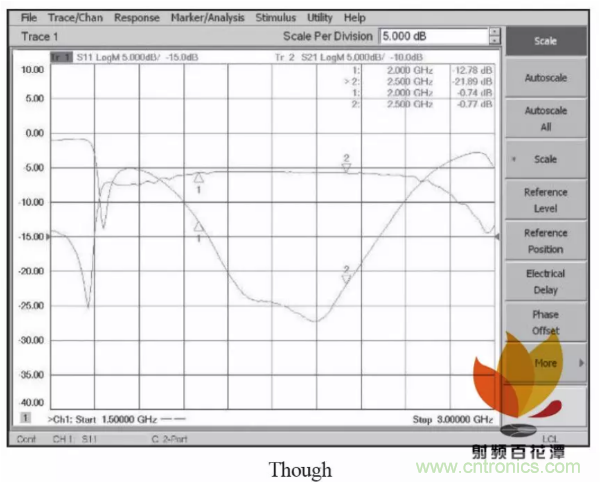

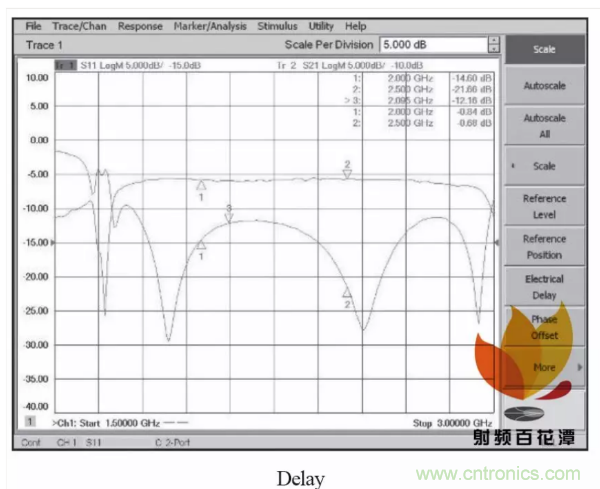

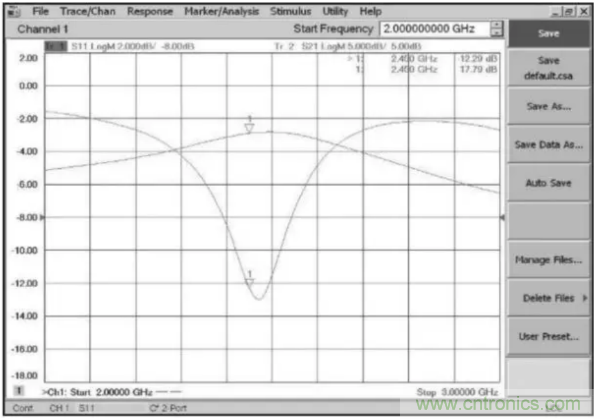

在完成TRL校準件的加工之后,我們將TRL校準件中的Though校準件和Delay校準件在Agilent的N5241A網(wǎng)絡分析儀上進行小信號參數(shù)的測試,采用其結果與仿真結果進行對比。圖4中上面的圖為“Though校準件”的S11和S21的頻率掃描圖,下面的圖為“Delay校準件”的S11和S21的頻率掃描圖。從結果來看,“Though校準件”和“Delay校準件”的S11最大值均低于-12dB,S21的最大值均高-0.84dB。其測量結果與仿真結果基本一致,從測試值來講還略優(yōu)于仿真的結果。

圖4:TRL校準件S參數(shù)實測

2、器件的校驗

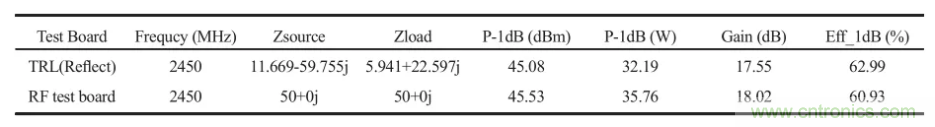

在此我們選取了一顆工作頻率在2.45GHz,功率30W的RF-LDMOS,并已在封裝內(nèi)完成輸入兩級匹配的器件來進行驗證。通過與Focus的Load-pull的校準和測量,我們得到的封裝器件的根部阻抗為:

輸入端:11.669 - 59.755j;

輸出端:5.941 + 22.597j

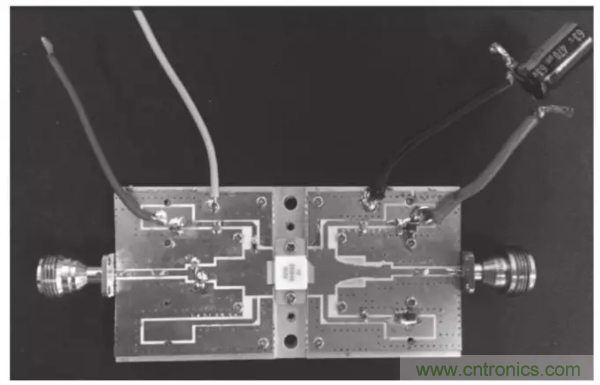

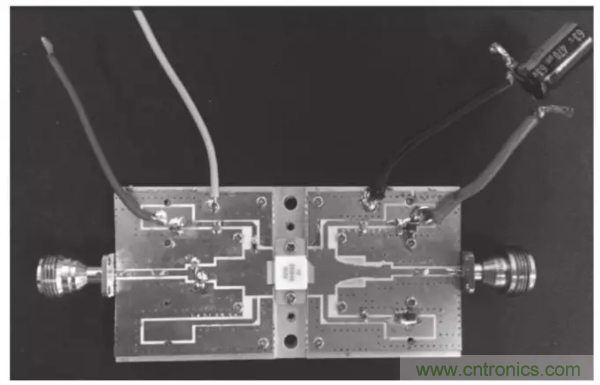

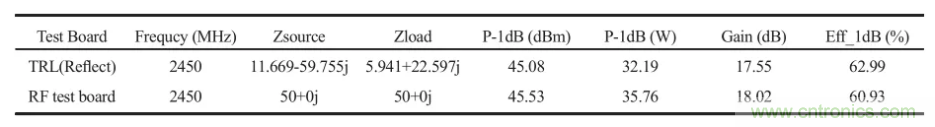

使用測量得到的器件根部的阻抗值,我們對符合器件的射頻電路測試板進行了匹配,見圖5。測試板的小信號測試曲線見圖6。對比使用TRL校準件得到的器件性能與射頻外圍電路測試板得到的器件性能,可以得出表3。

表3的數(shù)據(jù)顯示了使用TRL校準件測得的是器件根部阻抗以及在此阻抗下得到的器件性能。與根據(jù)根部阻抗進行的射頻電路測試板匹配后的器件性能比較,其增益、功率和效率基本一致。

圖5:24030器件射頻測試電路

圖6:TRL校準件小信號測試曲線

表3:TRL校準件得到的24030器件根部阻抗以及性能測試對比

結語

上文關于TRL校準件的設計和制作很好地完成了既定的目標,實現(xiàn)了高頻下射頻大功率器件的TRL校準,同時我們也看到,TRL校準件的設計涉及的很多方面和細節(jié)需要很好的梳理和把握。當然,一個好的TRL校準件的設計和制作還需要考慮更多的封裝的兼容以及更寬頻率的覆蓋,這個也是我們將要努力的方向。

本文轉(zhuǎn)載自:射頻百花譚

作者:李樹琪 蘇州遠創(chuàng)達

推薦閱讀: