【導(dǎo)讀】高分辨率數(shù)模轉(zhuǎn)換器(DAC)的常見用途之一是提供可控精密電壓��。分辨率高達(dá)20位�����、精度達(dá)1 ppm且具有合理速率的DAC的應(yīng)用范圍包括醫(yī)療MRI系統(tǒng)中的梯度線圈控制�、測(cè)試和計(jì)量中的精密直流源、質(zhì)譜測(cè)定和氣譜分析中的精密定點(diǎn)和位置控制以及科學(xué)應(yīng)用中的光束檢測(cè)�。

隨著時(shí)間的推移,半導(dǎo)體處理和片內(nèi)校準(zhǔn)技術(shù)的發(fā)展���,關(guān)于精密集成電路DAC的定義也不斷變化���。高精度12 位DAC一度被認(rèn)為遙不可及;近年來(lái)��,16 位精度已日益在精密醫(yī)學(xué)��、儀器儀表、測(cè)試和計(jì)量應(yīng)用中得到廣泛運(yùn)用�����;在未來(lái)�,控制系統(tǒng)和儀器儀表系統(tǒng)甚至需要更高的分辨率和精度。

高精密應(yīng)用目前要求18/20位�����、1 ppm精度數(shù)模轉(zhuǎn)換器�,以前只有笨重、昂貴�����、慢速的Kelvin-Varley分壓器才能達(dá)到這一性能水平—屬于標(biāo)準(zhǔn)實(shí)驗(yàn)室的專利�,幾乎不適用于現(xiàn)實(shí)儀器儀表系統(tǒng)。針對(duì)這類要求且采用IC DAC組件�,更便利的半導(dǎo)體1 ppm 精度解決方案已推出數(shù)年,但此類復(fù)雜系統(tǒng)需要使用多種器件�����,需要不斷進(jìn)行校準(zhǔn)���,還需十分謹(jǐn)慎才可取得理想精度���,而且體積大、成本高(見附錄)��。長(zhǎng)久以來(lái)����,精密儀器儀表市場(chǎng)都需要一種更簡(jiǎn)單,具有成本優(yōu)勢(shì)���,無(wú)需校準(zhǔn)或持續(xù)監(jiān)控��,簡(jiǎn)單易用��,而且提供保證性能規(guī)格的DAC�����。目前����,從16 位和18 位單芯片轉(zhuǎn)換器(如DAC)自然升級(jí)已成為可能�。

AD5791 1 ppm DAC

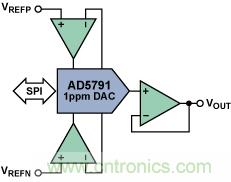

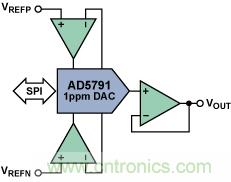

半導(dǎo)體處理技術(shù)、DAC架構(gòu)設(shè)計(jì)和快速片內(nèi)校準(zhǔn)技術(shù)的發(fā)展使穩(wěn)定、建立時(shí)間短的高線性度數(shù)模轉(zhuǎn)換器成為可能�。這種轉(zhuǎn)換器可提供高優(yōu)于1 ppm的相對(duì)精度、0.05 ppm/°C溫度漂移��、0.1 ppm p-p噪聲�����、優(yōu)于1 ppm的長(zhǎng)期穩(wěn)定性和1MHz吞吐量����。這類小型單芯片器件保證性能規(guī)格,無(wú)需校準(zhǔn)且簡(jiǎn)單易用�。AD5791及其配套基準(zhǔn)電壓源和輸出緩沖的典型功能框圖如圖1所示。

圖1:AD5791典型工作框圖����。

AD5791是一款單芯片、20 位�、電壓輸出數(shù)模轉(zhuǎn)換器,具有額定的1 LSB(最低有效位)積分非線性度(INL)和微分非線性度(DNL)�����,是業(yè)界首款單芯片1 ppm 精度的數(shù)模轉(zhuǎn)換器(1 LSB@20位為220分之一 =1,048,576分之一 = 1 ppm)��。該器件設(shè)計(jì)用于高精密儀器儀表以及測(cè)試和計(jì)量系統(tǒng),與其他解決方案相比���,其整體性能有較大提升,具有更高的精度�、體積更小、成本更低���,使以前不具經(jīng)濟(jì)可行性的儀器儀表應(yīng)用成為可能���。

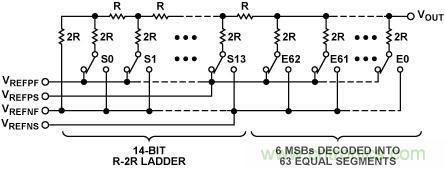

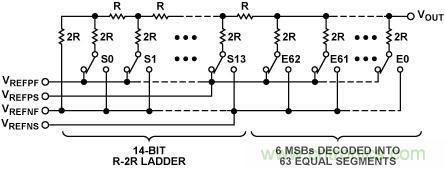

其設(shè)計(jì)(如圖2所示)采用精密電壓模式R-2R架構(gòu),利用了最新的薄膜電阻匹配技術(shù)����,并通過(guò)片內(nèi)校準(zhǔn)例程來(lái)實(shí)現(xiàn)1 ppm精度。由于AD5791采用工廠校準(zhǔn)模式���,因而運(yùn)行時(shí)無(wú)需校準(zhǔn)程序�,其延遲不超過(guò)100 ns��,可用于波形生成應(yīng)用及快速控制環(huán)路�。

圖2:DAC梯形結(jié)構(gòu)。

AD5791不但提供出色的線性度���,而且可具有9 nV/Hz噪聲密度��、0.1 Hz至10 Hz頻帶內(nèi)0.6 μV峰峰值噪聲����、0.05 ppm/°C溫度漂移,且其1000小時(shí)長(zhǎng)期穩(wěn)定性優(yōu)于0.1 ppm�����。

作為一種高電壓器件���,采用雙電源供電���,最高±16.5 V。輸出電壓范圍由正負(fù)基準(zhǔn)電壓VREFP 和VREFN決定��,提供了靈活的輸出范圍選擇�����。

AD5791 所用精密架構(gòu)要求使用高性能外置放大器來(lái)緩沖來(lái)自3.4 k? DAC電阻的基準(zhǔn)源�,為基準(zhǔn)輸入引腳的加載感應(yīng)提供方便,以確保AD5791的1 ppm線性度��。AD5791需要一個(gè)輸出緩沖來(lái)驅(qū)動(dòng)負(fù)載,以減輕3.4 k?輸出阻抗的負(fù)擔(dān)——除非驅(qū)動(dòng)的是一個(gè)極高阻抗�����、低電容負(fù)載——或者衰減處于容限之內(nèi)并可預(yù)測(cè)����。

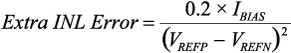

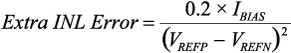

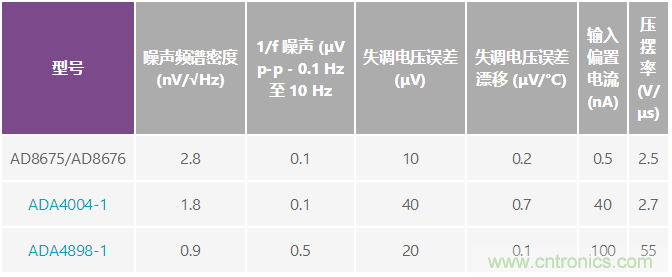

由于放大器為外置型��,可根據(jù)噪聲���、溫度漂移和速度的優(yōu)化需要進(jìn)行選擇——并可調(diào)整比例因子——具體視應(yīng)用需要而定�����。對(duì)于基準(zhǔn)緩沖����,建議采用AD8676 雙通道放大器�,其具有低噪聲、低失調(diào)誤差��、低失調(diào)誤差漂移和低輸入偏置電流的特點(diǎn)���?����;鶞?zhǔn)緩沖的輸入偏置電流特性非常重要��,因?yàn)檫^(guò)大的偏置電流會(huì)降低直流線性度����。積分非線性度的降低(單位:ppm)為輸入偏置電流的函數(shù),一般表示為:

其中���,IBIAS 單位為 nA; VREFP 和 VREFN 的單位均為伏特��。例如���,對(duì)于±10 V的基準(zhǔn)輸入范圍,100 nA的輸入偏置電流將使INL提高0.05 ppm�����。

輸出緩沖的主要要求與基準(zhǔn)緩沖相似——唯一例外是偏置電流���,因?yàn)樗挥绊慉D5791的線性度��。但失調(diào)電壓和輸入偏置電流可能會(huì)影響到輸出失調(diào)電壓�����。為了維持直流精度�����,建議將AD8675 用作輸出緩沖��。高吞吐量應(yīng)用要求使用較高壓擺率的快速輸出緩沖放大器���。

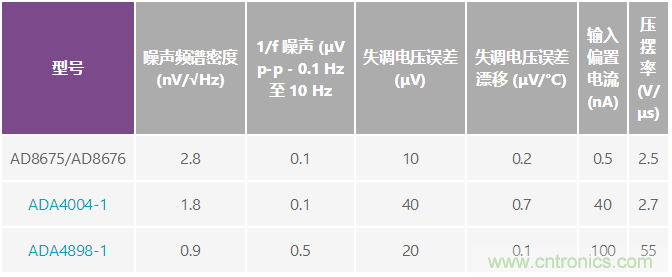

表1 列出了少數(shù)適用精密放大器的關(guān)鍵技術(shù)規(guī)格。

AD5791具有設(shè)計(jì)時(shí)間更短����、設(shè)計(jì)風(fēng)險(xiǎn)更小、成本更低����、電路板尺寸更小、可靠性更高和保證性能規(guī)格的特點(diǎn)��。

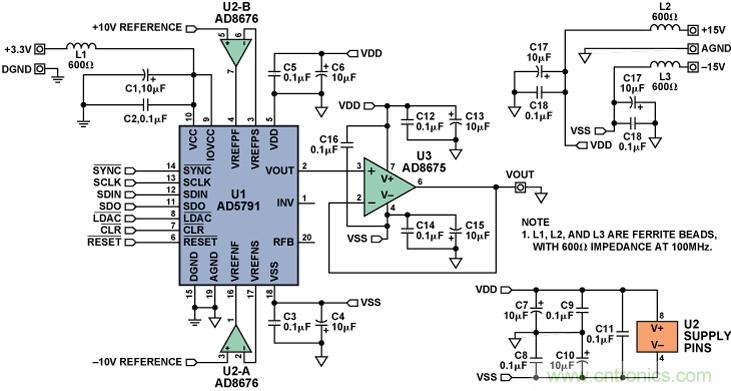

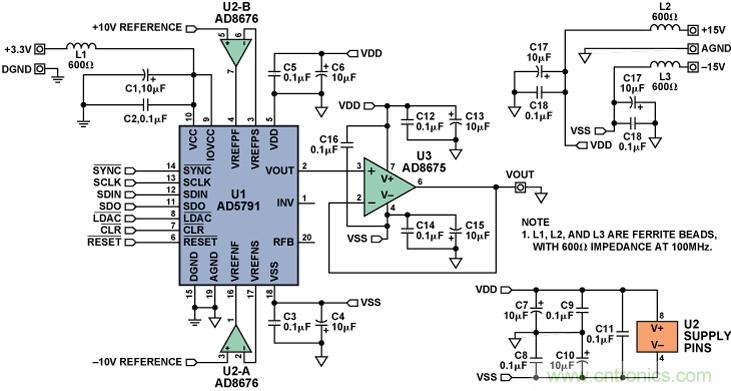

圖3是一種電路示意圖��,其中以AD5791 (U1)作為精密數(shù)控1 ppm電壓源,電壓范圍為±10V��,增量為20 μV��;以AD8676 (U2)作為基準(zhǔn)緩沖����;以AD8675 (U3)作為輸出緩沖。絕對(duì)精度取決于外置10 V基準(zhǔn)電壓源的選擇���。

圖3:采用AD5791數(shù)模轉(zhuǎn)換器的1 ppm精度系統(tǒng)����。

性能測(cè)量

該電路的重要指標(biāo)是積分非線性度��、微分非線性度和0.1 Hz至10 Hz峰峰值噪聲����。圖4顯示,典型INL處于±0.6 LSB之內(nèi)����。

圖4:積分非線性度坐標(biāo)圖。

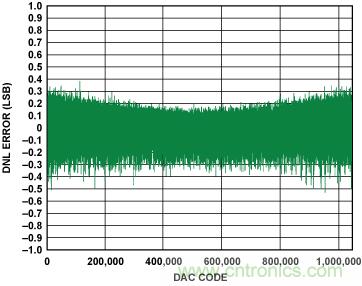

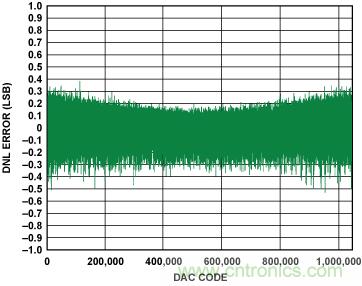

圖5所示典型DNL為±0.5 LSB;在整個(gè)位躍遷范圍內(nèi)��,輸出均可保證單調(diào)性����。

圖5:微分非線性度坐標(biāo)圖。

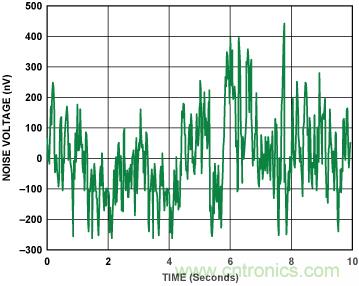

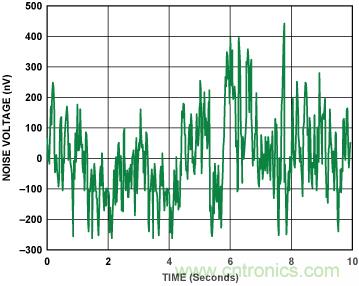

0.1 Hz至10 Hz帶寬內(nèi)的峰峰值噪聲約為700 nV��,如圖6所示�����。

圖6:低頻噪聲���。

AD5791僅僅是個(gè)開始:

1 ppm電路的復(fù)雜性

盡管AD5791一類的精密次 1 ppm元件已上市,但構(gòu)建1 ppm系統(tǒng)并非易事�,不能草率對(duì)待。必須全面考慮在這個(gè)精度級(jí)別出現(xiàn)的誤差源���。1 ppm 精度電路中的主要誤差源為噪聲��、溫度漂移����、熱電電壓和物理應(yīng)力。應(yīng)遵循精密電路的構(gòu)建技術(shù)����,以盡量降低此類誤差在整個(gè)電路中的耦合和傳播效應(yīng),避免產(chǎn)生外部干擾�。下面將簡(jiǎn)要總結(jié)這些考慮因素。更多詳情請(qǐng)參閱參考文獻(xiàn)���。

噪聲

工作于1 ppm分辨率和精度時(shí)����,必須將噪聲降至最低水平�。AD5791的噪聲頻譜密度為9 nV/Hz,主要源于3.4 k? DAC電阻的約翰遜噪聲�。為了盡量避免增加系統(tǒng)噪聲,必須將所有外設(shè)的噪聲貢獻(xiàn)降至最低��。電阻值應(yīng)低于DAC電阻���,以確保其約翰遜噪聲貢獻(xiàn)不會(huì)大幅提高方和根總體噪聲水平�。AD8676基準(zhǔn)緩沖和AD8675輸出緩沖額定噪聲密度為2.8 nV/Hz����,遠(yuǎn)遠(yuǎn)低于DAC的噪聲貢獻(xiàn)���。

通過(guò)簡(jiǎn)單的R-C濾波器,即可相對(duì)簡(jiǎn)單地消除高頻噪聲�����,但0.1 Hz至10 Hz范圍內(nèi)的1/f噪聲卻很難在不影響直流精度的情況下濾除�����。降低1/f噪聲最有效的方法是避免其進(jìn)入電路之中����。AD5791在0.1 Hz至10 Hz帶寬下產(chǎn)生約0.6 μV峰峰值噪聲,遠(yuǎn)低于1 LSB(輸出范圍為±10 V時(shí)��,1 LSB = 19 μV)�。在整個(gè)電路中,1/f最大噪聲的目標(biāo)值應(yīng)為0.1 LSB或2 μV左右����,通過(guò)選擇合適的元件即可達(dá)到此目標(biāo)�。電路中的放大器產(chǎn)生0.1 μV峰峰值1/f噪聲; 信號(hào)鏈中的三個(gè)放大器在電路輸出端共產(chǎn)生約0.2 μV峰峰值噪聲���。加上來(lái)自AD5791的0.6 μV峰峰值噪聲��,預(yù)計(jì)總1/f噪聲約為0.8 μV峰峰值����, 該值與圖5所示測(cè)量值緊密相關(guān)。這為可能增加的其他電路(如放大器���、電阻和基準(zhǔn)電壓源)等留出了充足的余量����。

除隨機(jī)噪聲以外�����,還須避免由輻射���、傳導(dǎo)和感應(yīng)電干擾導(dǎo)致的誤差���。必須采用屏蔽、防護(hù)����、謹(jǐn)慎接地�����、正確的印刷電路板布線等技術(shù)�。

溫度漂移

與所有精密電路一樣��,所有元件的溫度漂移是主要誤差源之一���。減少漂移的關(guān)鍵是選擇次 1 ppm溫度系數(shù)的重要元件�。AD5791具有極低的溫度系數(shù)����,為0.05 ppm/°C。AD8676基準(zhǔn)緩沖的漂移系數(shù)為0.6 μV/°C�����,總共會(huì)向電路中增0.03 ppm/°C的增益漂移��;AD8675輸出緩沖會(huì)再貢獻(xiàn)0.03 ppm/°C的輸出漂移�;相加后為0.11 ppm/°C?�?s放和增益電路中應(yīng)使用低漂移���、熱匹配電阻網(wǎng)絡(luò)�。建議使用Vishay體金屬薄膜分壓器電阻系列300144Z和300145��,其電阻跟蹤溫度系數(shù)為0.1 ppm/°C����。

熱電電壓

熱電電壓是Seebeck效應(yīng)造成的結(jié)果:相異金屬結(jié)處產(chǎn)生與溫度有關(guān)的電壓。根據(jù)結(jié)處的金屬元件�,結(jié)果產(chǎn)生的電壓位于0.2 μV/°C至1 mV/°C之間。最好的情況是銅銅結(jié)�����,產(chǎn)生的熱電EMF不到0.2 μV/°C�。在最糟糕的情況下,銅銅氧化物結(jié)可產(chǎn)生最大1 mV/°C的熱電電壓����。對(duì)小幅溫度波動(dòng)的這種靈敏度意味著,附近的耗能元件或跨越印刷電路板(PCB)的低速氣流可能產(chǎn)生不同的溫度梯度����,結(jié)果產(chǎn)生不同的熱電電壓,而這種電壓又表現(xiàn)為與低頻1/f 噪聲相似的低頻漂移���?��?赏ㄟ^(guò)消除系統(tǒng)中的相異結(jié)和/或消除熱梯度來(lái)避免熱電電壓�。雖然消除相異金屬結(jié)幾乎不可能——IC封裝��、PCB電路�����、布線和連接器中存在多種不同的金屬——但使所有連接均保持整潔����,消除氧化物,這種方法可以有效地減少熱電電壓����。屏蔽電路使其不受氣流影響,是一種有效的熱電電壓穩(wěn)定方法�,而且具有電屏蔽的增值作用。圖7展示了開放式電路與封閉式電路在電壓漂移上的差異�。

圖7:開放式系統(tǒng)和封閉式系統(tǒng)的電壓漂移與時(shí)間關(guān)系。

為了消除熱電電壓��,可在電路中增加補(bǔ)償結(jié),但必須進(jìn)行大量的試驗(yàn)和重復(fù)測(cè)試�����,以確保插入結(jié)配對(duì)正確����、位置無(wú)誤�。截至目前,最高效的方法是減少信號(hào)路徑中的元件數(shù)����,穩(wěn)定局部溫度和環(huán)境溫度,從而減少電路中的結(jié)���。

物理應(yīng)力

高精模擬半導(dǎo)體器件對(duì)其封裝承受的應(yīng)力非常敏感���。封裝中的應(yīng)力消除填充物具有一定的作用,但無(wú)法補(bǔ)償因PCB變形等局部應(yīng)力源在封裝上直接產(chǎn)生的壓力帶來(lái)的較大應(yīng)力��。印刷電路板越大����,封裝可能承受的應(yīng)力越大,因此即使在小型電路板上也應(yīng)安裝敏感電路——通過(guò)柔性或非剛性連接器與大系統(tǒng)相連��。如果必須使用較大電路板,則應(yīng)在敏感元件周圍��,在元件兩面或(最好)三面割些應(yīng)力消除切口�,可極大地減少因電路板彎曲給元件帶來(lái)的應(yīng)力。

長(zhǎng)期穩(wěn)定性

在考慮噪聲和溫度漂移的基礎(chǔ)上��,還需考慮長(zhǎng)期穩(wěn)定性����。精密模擬IC雖然非常穩(wěn)定,但確實(shí)會(huì)發(fā)生長(zhǎng)期老化變化�����。AD5791在125°C的長(zhǎng)期穩(wěn)定性一般好于0.1 ppm/1000 小時(shí)�����。雖然老化不具累積性質(zhì)����,但遵循平方根規(guī)則(若某個(gè)器件的老化速度為1 ppm/1000 小時(shí),為2 ppm/2000 小時(shí)��,為3 ppm/3000 小時(shí)等等)。一般地��,溫度每降低25°C���,時(shí)間就會(huì)延長(zhǎng)10倍�����;因此,當(dāng)工作溫度為85°C時(shí)��,在10000小時(shí)的期間(約60星期)����,預(yù)計(jì)老化為0.1 ppm。以此外推��,在10年期間�,預(yù)計(jì)老化為0.32 ppm。即是說(shuō)�����,當(dāng)工作溫度為85°C時(shí)�,在10年期間,數(shù)據(jù)手冊(cè)直流規(guī)格可能漂移0.32 ppm。

電路構(gòu)建和布局

在注重精度的電路中���,精心考慮電源和接地回路布局有助于確保達(dá)到額定性能�。在設(shè)計(jì)PCB時(shí)�,應(yīng)采用模擬部分與數(shù)字部分相分離的設(shè)計(jì),并限制在電路板的不同區(qū)域內(nèi)�。如果DAC所在系統(tǒng)中有多個(gè)器件要求模數(shù)接地連接,則只能在一個(gè)點(diǎn)上進(jìn)行連接�����。星形接地點(diǎn)盡可能靠近該器件��。必須采用足夠大的10 μF電源旁路電容����,與每個(gè)電源引腳上的0.1 μF電容并聯(lián),并且盡可能靠近封裝���,最好是正對(duì)著該器件����。10 μF電容應(yīng)為鉭珠型電容�����。0.1 μF電容必須具有低有效串聯(lián)電阻(ESR)和低有效串聯(lián)電感(ESL),如高頻時(shí)提供低阻抗接地路徑的普通多層陶瓷型電容�����,以便處理內(nèi)部邏輯開關(guān)所引起的瞬態(tài)電流�����。各電源線路上若串聯(lián)一個(gè)鐵氧體磁珠����,則可進(jìn)一步防止高頻噪聲通過(guò)器件����。

電源走線必須盡可能寬,以提供低阻抗路徑�����,并減小電源線路上的毛刺效應(yīng)�����。利用數(shù)字地將快速開關(guān)信號(hào)(如時(shí)鐘)屏蔽起來(lái),以避免向電路板上的其他器件輻射噪聲����,并且不得靠近基準(zhǔn)輸入,也不得置于封裝之下�����?�;鶞?zhǔn)輸入上的噪聲必須降至最低��,因?yàn)檫@種噪聲會(huì)被耦合至DAC輸出�����。避免數(shù)字信號(hào)與模擬信號(hào)交叉�����,電路板相反兩側(cè)上的走線應(yīng)彼此垂直�����,以減小電路板的饋通效應(yīng)��。

基準(zhǔn)電壓源

維持整個(gè)電路性能的是外部基準(zhǔn)電壓源,其噪聲和溫度系數(shù)直接影響系統(tǒng)的絕對(duì)精度�����。為了充分發(fā)揮1 ppm AD5791數(shù)模轉(zhuǎn)換器的性能�����,基準(zhǔn)元件和關(guān)聯(lián)元件應(yīng)具有與DAC不相上下的溫度漂移和噪聲規(guī)格��。雖然離溫度漂移為0.05 ppm/°C的基準(zhǔn)電壓源仍相去甚遠(yuǎn)���,但0.1 Hz 至10 Hz范圍噪聲低于1 μV p-p的1 ppm/°C和2 ppm/°C基準(zhǔn)電壓源確實(shí)存在��。

結(jié)論

隨著精密儀器儀表以及測(cè)試和計(jì)量應(yīng)用對(duì)精度的要求不斷提高��,人們正在開發(fā)精度更高的元件,以滿足這些需求����。此類器件具有1 ppm級(jí)精度規(guī)格,用戶無(wú)需進(jìn)一步校準(zhǔn)�����,而且簡(jiǎn)單易用。然而��,在設(shè)計(jì)這一精度級(jí)別的電路時(shí)�����,必須考慮多種現(xiàn)實(shí)環(huán)境因素和設(shè)計(jì)相關(guān)因素����。精密電路性能的成功與否取決于對(duì)這些因素的考慮和理解是否到位,取決于選擇正確的元件�����。

參考電路

(有關(guān)全部ADI元件的詳細(xì)信息�����,請(qǐng)?jiān)L問 www.analog.com.)

1. "The Long Term Stability of Precision Analog ICs, or How to Age Gracefully and Avoid Sudden Death." Analog Devices. Rarely Asked Questions.

http://www.analog.com/en/analog-dialogue/raqs/2016/03/09/14/49/raq-issue-15.html.

2. Low Level Measurements Handbook. 6th Edition. Keithley. 2004.

http://www.tek.com/document/primer/low-level-measurements-handbook-precision-dc-current-voltage-and-resistance-measurem.

3. MT-031, Grounding Data Converters and Solving the Mystery of "AGND" and "DGND."

http://www.analog.com/static/imported-files/tutorials/MT-031.pdf.

附錄

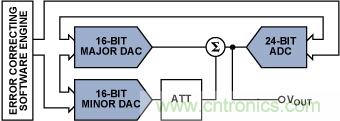

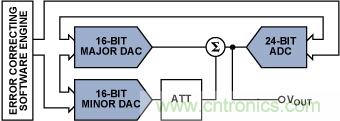

圖8所示為一種典型的現(xiàn)代1 ppm DAC解決方案的功能框圖��。電路核心由兩個(gè)16 位數(shù)模轉(zhuǎn)換器構(gòu)成——一個(gè)主DAC和一個(gè)輔助DAC——其輸出經(jīng)縮放和組合后產(chǎn)生更高的分辨率�����。主DAC輸出與經(jīng)衰減的輔助DAC輸出相加��,使輔助DAC填補(bǔ)主DAC LSB步長(zhǎng)之間的分辨率間隙。

圖8. 分立1 ppm DAC解決方案���。

組合后的DAC輸出需要為單調(diào)性���,但線性度無(wú)需極高,因?yàn)楦咝阅苁峭ㄟ^(guò)精密模數(shù)轉(zhuǎn)換器的恒定電壓反饋取得的�,該轉(zhuǎn)換器校正固有的元件誤差;電路精度受ADC的限制而不受限于DAC�。然而,由于恒定電壓反饋的要求以及不可避免的環(huán)路延遲�,這種解決方案速度較慢,建立時(shí)間達(dá)數(shù)秒����。

盡管這種電路能夠并且經(jīng)努力可以取得1 ppm的精度,但設(shè)計(jì)難度較大���,很可能需要重復(fù)設(shè)計(jì)多次�,而且需要通過(guò)軟件引擎和精密ADC來(lái)實(shí)現(xiàn)目標(biāo)精度�。為了保證1 ppm的精度�����,ADC還需進(jìn)行校準(zhǔn),因?yàn)槟壳笆袌?chǎng)上還沒有保證1 ppm線性度的ADC�。圖8所示簡(jiǎn)圖只是概念的展示,真實(shí)的電路要復(fù)雜得多�����,涉及多個(gè)增益����、衰減和求和級(jí),包括多個(gè)元件�。同時(shí)還需要復(fù)雜的數(shù)字電路,以方便DAC與ADC之間的接口���,更不用說(shuō)用于誤差校正的軟件了�。

推薦閱讀: