【導(dǎo)讀】在電路板設(shè)計中,噪聲問題是每位設(shè)計師都會遇到的一大問題。為了解決噪聲問題,一般需要花費數(shù)小時時間來進行實驗室測試才能揪出真正的元兇。然而很多時候我們卻發(fā)現(xiàn),噪聲問題是由開關(guān)電源的布局不當(dāng)而引起的。該怎么解決此類問題呢?

小A:這份PCB布局布線指南,請收好~

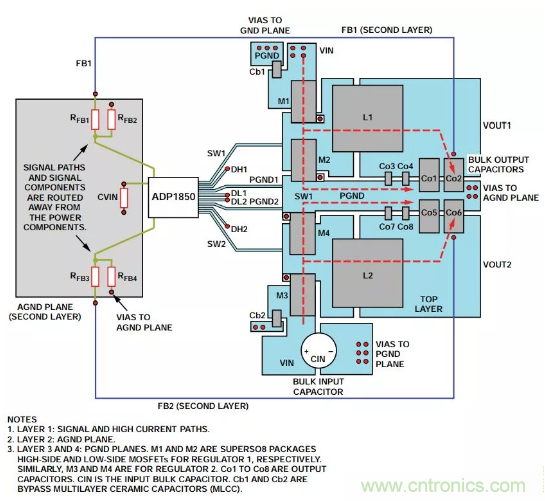

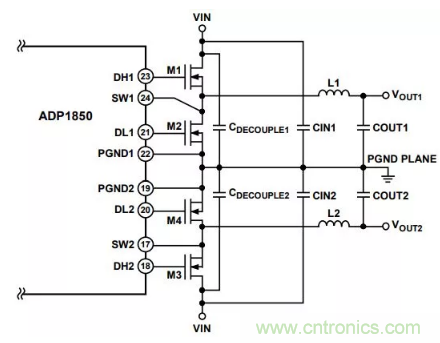

作為例子的開關(guān)調(diào)節(jié)器布局采用雙通道同步開關(guān)控制器 ADP1850,第一步是確定調(diào)節(jié)器的電流路徑。然后,進行物理規(guī)劃和電源器件的考慮。此外,我們需要了解一點:電流路徑?jīng)Q定了器件在該低噪聲布局布線設(shè)計中的位置。

調(diào)節(jié)器的電流路徑

在開關(guān)轉(zhuǎn)換器設(shè)計中,高電流路徑和低電流路徑彼此非??拷?。交流(AC)路徑攜帶有尖峰和噪聲,高直流(DC)路徑會產(chǎn)生相當(dāng)大的壓降,低電流路徑往往對噪聲很敏感。適當(dāng)PCB布局布線的關(guān)鍵在于確定關(guān)鍵路徑,然后安排器件,并提供足夠的銅面積以免高電流破壞低電流。性能不佳的表現(xiàn)是接地反彈和噪聲注入IC及系統(tǒng)的其余部分。

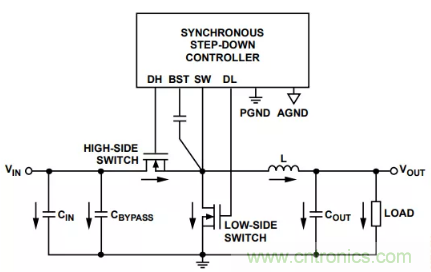

圖1所示為一個同步降壓調(diào)節(jié)器設(shè)計,它包括一個開關(guān)控制器和以下外部電源器件:高端開關(guān)、低端開關(guān)、電感、輸入電容、輸出電容和旁路電容。圖1中的箭頭表示高開關(guān)電流流向。必須小心放置這些電源器件,避免產(chǎn)生不良的寄生電容和電感,導(dǎo)致過大噪聲、過沖、響鈴振蕩和接地反彈。

圖1:典型開關(guān)調(diào)節(jié)器(顯示交流和直流電流路徑)

諸如DH、DL、BST和SW之類的開關(guān)電流路徑離開控制器后需妥善安排,避免產(chǎn)生過大寄生電感。這些線路承載的高δI/δt交流開關(guān)脈沖電流可能達(dá)到3 A以上并持續(xù)數(shù)納秒。高電流環(huán)路必須很小,以盡可能降低輸出響鈴振蕩,并且避免拾取額外的噪聲。

低值、低幅度信號路徑,如補償和反饋器件等,對噪聲很敏感。應(yīng)讓這些路徑遠(yuǎn)離開關(guān)節(jié)點和電源器件,以免注入干擾噪聲。

布局物理規(guī)劃

PCB物理規(guī)劃(floor plan)非常重要,必須使電流環(huán)路面積最小,并且合理安排電源器件,使得電流順暢流動,避免尖角和窄小的路徑。這將有助于減小寄生電容和電感,從而消除接地反彈。

圖2所示為采用開關(guān)控制器ADP1850的雙路輸出降壓轉(zhuǎn)換器的PCB布局。請注意,電源器件的布局將電流環(huán)路面積和寄生電感降至最小。虛線表示高電流路徑。同步和異步控制器均可以使用這一物理規(guī)劃技術(shù)。在異步控制器設(shè)計中,肖特基二極管取代低端開關(guān)。

圖2:采用ADP1850控制器的雙路輸出降壓轉(zhuǎn)換器的PCB布局

電源器件:MOSFET和電容

頂部和底部電源開關(guān)處的電流波形是一個具有非常高δI/δt的脈沖。因此,連接各開關(guān)的路徑應(yīng)盡可能短,以盡量降低控制器拾取的噪聲和電感環(huán)路傳輸?shù)脑肼暋T赑CB一側(cè)上使用一對DPAK或SO-8封裝的FET時,最好沿相反方向旋轉(zhuǎn)這兩個FET,使得開關(guān)節(jié)點位于該對FET的一側(cè),并利用合適的陶瓷旁路電容將高端漏電流旁路到低端源。務(wù)必將旁路電容盡可能靠近MOSFET放置(參見圖2),以盡量減小穿過FET和電容的環(huán)路周圍的電感。

輸入旁路電容和輸入大電容的放置對于控制接地反彈至關(guān)重要。輸出濾波器電容的負(fù)端連接應(yīng)盡可能靠近低端 MOSFET的源,這有助于減小引起接地反彈的環(huán)路電感。圖2中的Cb1和Cb2是陶瓷旁路電容,這些電容的推薦值范圍是1 μF至22 μF。對于高電流應(yīng)用,應(yīng)額外并聯(lián)一個較大值的濾波器電容,如圖2的CIN所示。

散熱考慮和接地層

在重載條件下,功率MOSFET、電感和大電容的等效串聯(lián)電阻(ESR)會產(chǎn)生大量的熱。為了有效散熱,圖2的示例在這些電源器件下面放置了大面積的銅。

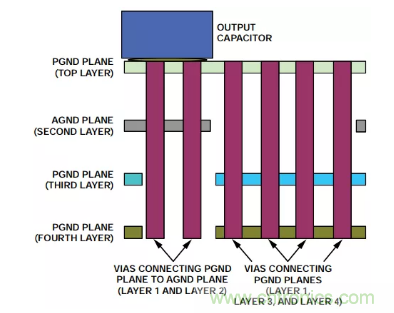

多層PCB的散熱效果好于2層PCB。為了提高散熱和導(dǎo)電性能,應(yīng)在標(biāo)準(zhǔn)1盎司銅層上使用2盎司厚度的銅。多個 PGND層通過過孔連在一起也會有幫助。圖3顯示一個4層 PCB設(shè)計的頂層、第三層和第四層上均分布有PGND層。

圖3:截面圖:連接PGND層以改善散熱

這種多接地層方法能夠隔離對噪聲敏感的信號。如圖2所 示,補償器件、軟啟動電容、偏置輸入旁路電容和輸出反饋分壓器電阻的負(fù)端全都連接到AGND層。請勿直接將任何高電流或高δI/δt路徑連接到隔離AGND層。AGND是一個安靜的接地層,其中沒有大電流流過。

所有電源器件(如低端開關(guān)、旁路電容、輸入和輸出電容等)的負(fù)端連接到PGND層,該層承載高電流。

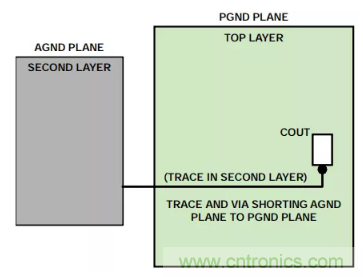

GND層內(nèi)的壓降可能相當(dāng)大,以至于影響輸出精度。通過一條寬走線將AGND層連接到輸出電容的負(fù)端(參見圖4),可以顯著改善輸出精度和負(fù)載調(diào)節(jié)。

圖4:AGND層到PGND層的連接

AGND層一路擴展到輸出電容,AGND層和PGND層在輸出電容的負(fù)端連接到過孔。

圖2顯示了另一種連接AGND和PGND層的技術(shù),AGND層通過輸出大電容負(fù)端附近的過孔連接到PGND層。圖3顯示了PCB上某個位置的截面,AGND層和PGND層通過輸出大電容負(fù)端附近的過孔相連。

電流檢測路徑

為了避免干擾噪聲引起精度下降,電流模式開關(guān)調(diào)節(jié)器的電流檢測路徑布局必須妥當(dāng)。雙通道應(yīng)用尤其要更加重視,消除任何通道間串?dāng)_。

雙通道降壓控制器ADP1850將低端MOSFET的導(dǎo)通電阻RDS(ON)用作控制環(huán)路架構(gòu)的一部分。此架構(gòu)在SWx與 PGNDx引腳之間檢測流經(jīng)低端MOSFET的電流。一個通道中的地電流噪聲可能會耦合到相鄰?fù)ǖ乐?。因此,?wù)必使 SWx和PGNDx走線盡可能短,并將其放在靠近MOSFET的地方,以便精確檢測電流。到SWx和PGNDx節(jié)點的連接務(wù)必采用開爾文檢測技術(shù),如圖2和圖5所示。注意,相應(yīng)的 PGNDx走線連接到低端MOSFET的源。不要隨意將PGND 層連接到PGNDx引腳。

圖5:兩個通道的接地技術(shù)

相比之下,對于ADP1829等雙通道電壓模式控制器,PGND1和PGND2引腳則是直接通過過孔連接到PGND層。

反饋和限流檢測路徑

反饋(FB)和限流(ILIM)引腳是低信號電平輸入,因此,它們對容性和感性噪聲干擾敏感。FB和ILIM走線應(yīng)避免靠近高δI/δt走線。注意不要讓走線形成環(huán)路,導(dǎo)致不良電感增加。在ILIM和PGND引腳之間增加一個小MLCC去耦電容 (如22 pF),有助于對噪聲進行進一步濾波。

開關(guān)節(jié)點

在開關(guān)調(diào)節(jié)器電路中,開關(guān)(SW)節(jié)點是噪聲最高的地方,因為它承載著很大的交流和直流電壓/電流。此SW節(jié)點需要較大面積的銅來盡可能降低阻性壓降。將MOSFET和電感彼此靠近放在銅層上,可以使串聯(lián)電阻和電感最小。

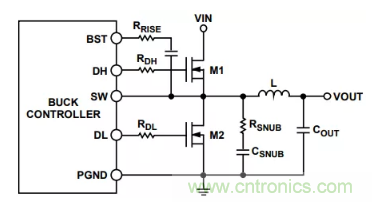

對電磁干擾、開關(guān)節(jié)點噪聲和響鈴振蕩更敏感的應(yīng)用可以使用一個小緩沖器。緩沖器由電阻和電容串聯(lián)而成(參見圖 6中的RSNUB和CSNUB),放在SW節(jié)點與PGND層之間,可以降 低SW節(jié)點上的響鈴振蕩和電磁干擾。注意,增加緩沖器可能會使整體效率略微下降0.2%到0.4%。

圖6:緩沖器和柵極電阻電阻

柵極驅(qū)動器路徑

柵極驅(qū)動走線(DH和DL)也要處理高δI/δt,往往會產(chǎn)生響鈴振蕩和過沖。這些走線應(yīng)盡可能短。最好直接布線,避免使用饋通過孔。如果必須使用過孔,則每條走線應(yīng)使用兩個過孔,以降低峰值電流密度和寄生電感。

在DH或DL引腳上串聯(lián)一個小電阻(約2 Ω至4 Ω)可以減慢柵極驅(qū)動,從而也能降低柵極噪聲和過沖。另外,BST與SW 引腳之間也可以連接一個電阻(參見圖6)。在布局期間用0 Ω柵極電阻保留空間,可以提高日后進行評估的靈活性。增加的柵極電阻會延長柵極電荷上升和下降時間,導(dǎo)致 MOSFET的開關(guān)功率損耗提高。

了解電流路徑、其敏感性以及適當(dāng)?shù)钠骷胖?,是消?PCB布局設(shè)計噪聲問題的關(guān)鍵。ADI公司的所有電源器件評估板都采用上述布局布線指導(dǎo)原則來實現(xiàn)最佳性能。評估板文件UG-204和UG-205詳細(xì)說明了ADP1850相關(guān)的布局布線情況。

注意

所有開關(guān)電源都具有相同的元件和相似的電流路徑敏感性。因此,以針對電流模式降壓調(diào)節(jié)器的 ADP1850為 例說明的指導(dǎo)原則同樣適用于電壓模式和/或升壓開關(guān)調(diào)節(jié)器的布局布線。

來源:ADI