【導讀】FPGA即現(xiàn)場可編程門陣列,它是作為專用集成電路(ASIC)領域中的一種半定制電路而出現(xiàn)的,既解決了定制電路的不足,又克服了原有可編程器件門電路數(shù)有限的缺點。對于時序如何用FPGA來分析與設計,本文將詳細介紹。

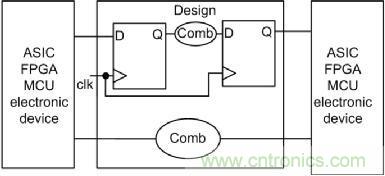

基本的電子系統(tǒng)如圖 1所示,一般自己的設計都需要時序分析,如圖 1所示的Design,上部分為時序組合邏輯,下部分只有組合邏輯。而對其進行時序分析時,一般都以時鐘為參考的,因此一般主要分析上半部分。在進行時序分析之前,需要了解時序分析的一些基本概念,如時鐘抖動、時鐘偏斜(Tskew)、建立時間(Tsu)、保持時間(Th)等。時序分析也就是分析每一個觸發(fā)器(寄存器)是否滿足建立時間/保持時間,而時序的設計的實質(zhì)就是滿足每一個觸發(fā)器的建立時間/保持時間的要求。

圖1.基本的電子系統(tǒng)

一、時鐘抖動和時鐘偏斜

1.時鐘抖動

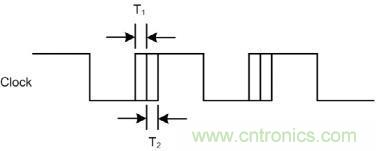

時鐘信號邊沿變化的不確定時間稱為時鐘抖動,如圖 2所示。一般情況下的時序分析是不考慮時鐘抖動,如果考慮時鐘抖動,則建立時間應該是Tsu+T1,保持時間應該是Th+T2。

圖2.時鐘抖動時序圖

2.時鐘偏斜

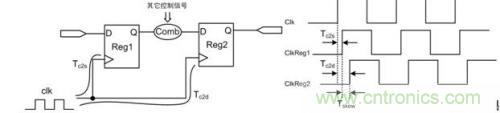

時序偏斜分析圖如圖 3所示。時鐘的分析起點是源寄存器(Reg1),終點是目標寄存器(Reg2)。時鐘在圖中的結(jié)構中傳輸也會有延遲,時鐘信號從時鐘源傳輸?shù)皆醇拇嫫鞯难訒r為Tc2s,傳輸?shù)侥繕思拇嫫鞯难訒r為Tc2d。時鐘網(wǎng)絡的延時為Tc2s與Tc2d之差,即Tskew=Tc2d-Tc2s。

圖3.時鐘偏斜時序圖

二、建立時間和保持時間

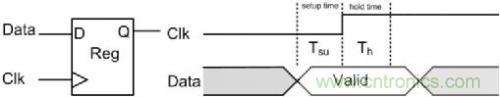

建立時間(Setup Time)常用Tsu表示,指的是在觸發(fā)器的時鐘信號上升沿到來以前,數(shù)據(jù)和使能信號穩(wěn)定不變的時間,如果建立時間不夠,數(shù)據(jù)將不能在這個時鐘上升沿被打入觸發(fā)器,使能信號無效,也就是說在這個時鐘周期對數(shù)據(jù)的操作時無效的;保持時間(Hold Time)常用Th表示,指的是在觸發(fā)器的時鐘信號上升沿到來以后,數(shù)據(jù)和使能信號穩(wěn)定不變的時間,如果保持時間不夠,數(shù)據(jù)同樣不能被打入觸發(fā)器,對數(shù)據(jù)的操作同樣是無效的,使能信號無效。數(shù)據(jù)要能穩(wěn)定傳輸,就必須滿足建立時間和保持時間的關系,圖 4標識了它們間的關系。

圖4.建立時間/操持時間的概念

三、發(fā)送沿和捕獲沿

(1)發(fā)送沿(Launch Edge):前級寄存器發(fā)送數(shù)據(jù)對應的時鐘沿,是時序分析的起點;

(2)捕獲沿(Latch Edge):后記寄存器捕獲數(shù)據(jù)對應的時鐘沿,是時序分析的終點。相對于launch Edge通常為一個時鐘周期,但不絕對,如多周期。

“信號跳變抵達窗口”:對latch寄存器來說,從previous時鐘對應的Hold Time開始,到current 時鐘對應的Setup Time 結(jié)束。

“信號電平采樣窗口”:對latch寄存器來說,從current時鐘對應的Setup Time開始,到current時鐘對應的Hold Time結(jié)束。

launch寄存器必須保證驅(qū)動的信號跳變到達latch寄存器的時刻處于“信號跳變抵達窗口”內(nèi),才能保證不破壞latch寄存器的“信號電平采樣窗口”。

圖5.Launch Edge和Latch Edge

四、數(shù)據(jù)和時鐘的時序分析

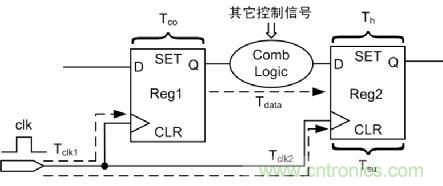

如圖 6所示,為分析建立時間/保持時間的基本電路圖。Tclk1為Reg1的時鐘延時,Tclk2為Reg2的時鐘延時,Tco為Reg1固有延時,Tdata為Reg1的到Reg2之間組合邏輯的延時,Tsu為Reg2的建立時間,Th為Reg2的保持時間,設時鐘clk周期為T,這里分析數(shù)據(jù)的建立時間和保持時間。

圖6.基本電路圖

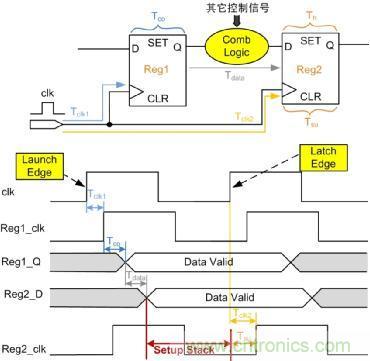

1、建立時間的分析

如圖 7所示,建立時間的分析是以第一個launch Edge為基準,在Latch Edge查看結(jié)果。建立時間的裕量(T為時鐘周期):

Setup Stack = (T+Tclk2) – Tsu – (Tclk1+Tco+Tdata)

假設△T = Tclk2-Tclk1,則:

Setup Stack = (T+△T) – Tsu – (Tco+Tdata)

可見△T<0影響建立時間,使建立時間的要求更加苛刻。因此對于△T盡量避免,采用同步單時鐘,并且盡量采用全局的時鐘信號,這樣△T幾乎為0,,△T的影響幾乎不存在,可以忽略不計。

如果建立時間的裕量Setup Stack小于0,則不滿足建立時間,也就會產(chǎn)生不穩(wěn)定態(tài),并通過寄存器傳輸下去。

圖7.建立時間時序分析圖

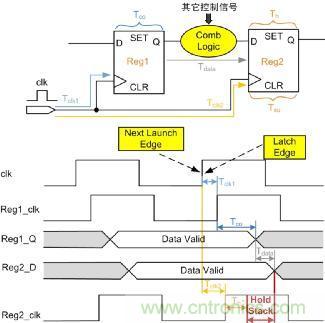

2、保持時間的分析

如圖 8所示,保持時間的分析是以第二個launch Edge為基準,在Latch Edge查看結(jié)果。保持時間的裕量:

Hold Stack = (Tclk1+Tco+Tdata) – Tclk2 – Th

假設△T = Tclk2-Tclk1,則:

Hold Stack = (Tco+Tdata) – △T – Th

可見△T>0影響保持時間,使保持時間的要求更加苛刻。。因此對于△T盡量避免,采用同步單時鐘,并且盡量采用全局的時鐘信號,這樣△T幾乎為0,,△T的影響幾乎不存在,可以忽略不計。

如果保持時間的裕量Hold Stack小于0,則不滿足保持時間,也就會產(chǎn)生不穩(wěn)定態(tài),并通過寄存器傳輸下去。

圖8.保持時間時序分析圖

五、DT6000S項目實例

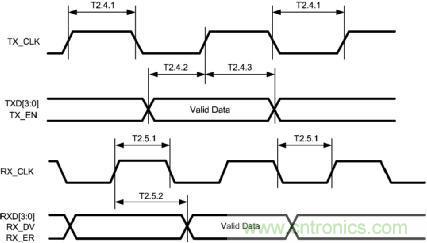

DT6000S項目上有4路光以太網(wǎng)接口連接到FPGA,由FPGA進行實現(xiàn)MAC層和解碼IEC61850的SV和GOOSE。以太網(wǎng)PHY通過MII接口和FPGA,因此FPGA與外部的接口有4路MII接口。項目初期是實現(xiàn)1路光以太網(wǎng)接口,并且驗證功能正確之后,但是后期變成的4路光以太網(wǎng)時,總會存在1路光以太網(wǎng)通信不正常。經(jīng)過分析得到是FPGA通MII接口和PHY的時序不滿足。如圖 9所示為MII接口的時序圖,時序不滿足分為TX_CLK和RX_CLK。

其一是PHY輸出的TX_CLK和FPGA依據(jù)TX_CLK產(chǎn)生的TXD[3:0]&TX_EN延時大,主要延時為內(nèi)部邏輯的延時,PCB延時小并且一致,導致PHY的TX_CLK的建立時間不滿足,從而導致發(fā)送數(shù)據(jù)錯誤。

其二是PHY輸出的RX_CLK和RXD[3:0]&RX_DV&RX_ER到FPGA內(nèi)部同步觸發(fā)器的延時之差太大,導致FPGA內(nèi)部同步觸發(fā)器的RX_CLK的建立時間不滿足,從而導致接收數(shù)據(jù)錯誤。

因此FPGA在綜合時需要添加約束,使之時序滿足要求,約束的條件為TXD[3:0]和TX_EN的輸出延時要少。RX_CLK和RXD[3:0]&RX_DV&RX_ER路徑延時之差要小。添加約束之后,4路MII接口的光以太網(wǎng)數(shù)據(jù)通信就正常了。

圖9.MII時序圖

這里闡述了時序分析基礎,說明概念的同時進行了時序分析,通過時序分析理解建立時間和保持時間。希望大家閱讀本文之后可以對FPGA時序分析有進一步的了解。