【導(dǎo)讀】工程師都知道,電子器件的電源測(cè)量通常是指開關(guān)電源的測(cè)量����,當(dāng)然也包括線性電源�。本文講解PWM開關(guān)電源����,而且僅僅是作為測(cè)試經(jīng)驗(yàn)的總結(jié)���,為大家簡述一些容易引起系統(tǒng)失效的因素。因此�,在閱讀本文之前,需要對(duì)開關(guān)電源有一定的了解����。

開關(guān)電源是一種高頻電能轉(zhuǎn)換裝置����,能將電壓透過不同形式的架構(gòu)轉(zhuǎn)換為用戶端所需求的電壓或電流����。開關(guān)電源的拓?fù)渲搁_關(guān)電源電路的構(gòu)成形式。一般是根據(jù)輸出地線與輸入地線有無電氣隔離�,分為隔離及非隔離變換器。

非隔離即輸入端與輸出端相通����,沒有隔離措施,常見的DC/DC變換器大多是這種類型�。所謂隔離是指輸入端與輸出端在電路上不是直接聯(lián)通的,使用隔離變壓器通過電磁變換方式進(jìn)行能量傳遞����,輸入端和輸出端之間是完全電氣隔離的。

對(duì)于開關(guān)變換器來說��,只有三種基本拓?fù)湫问?,即?/span>

Buck(降壓)

Boost(升壓)

Buck-Boost(升降壓)

三種基本拓?fù)湫问剑请姼械倪B接方式?jīng)Q定�。若電感放置于輸出端,則為Buck拓?fù)洌浑姼蟹胖糜谳斎攵?,則是Boost拓?fù)洹.?dāng)電感連接到地時(shí)�,就是Buck-Boost拓?fù)洹?/span>

容易引發(fā)系統(tǒng)失效的關(guān)鍵參數(shù)測(cè)試

以下的測(cè)試項(xiàng)目除了是指在靜態(tài)負(fù)載的情況下測(cè)試的結(jié)果,只有噪聲(noise)測(cè)試需要用到動(dòng)態(tài)負(fù)載�。

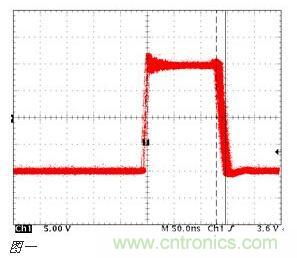

1.Phase點(diǎn)的jitter

對(duì)于典型的PWM開關(guān)電源,如果phase點(diǎn)jitter太大���,通常系統(tǒng)會(huì)不穩(wěn)定(和后面提到的相位裕量相關(guān))���,對(duì)于200~500K的PWM開關(guān)電源,典型的jitter值應(yīng)該在1ns以下����。

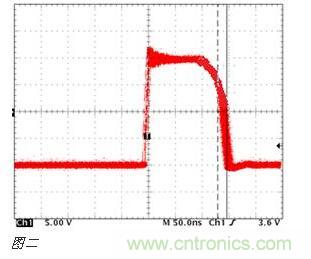

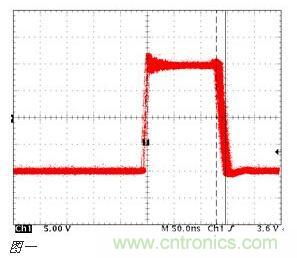

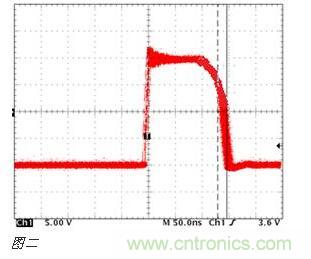

2. Phase點(diǎn)的塌陷

有時(shí)候工程師測(cè)量到下面的波形,這是典型的電感飽和的現(xiàn)象�。對(duì)于經(jīng)驗(yàn)不夠豐富的工程師,往往會(huì)忽略掉����。電感飽和會(huì)讓電感值急劇下降��,類似于短路了���,這樣會(huì)造成電流的急劇增加��,MOS管往往會(huì)因?yàn)闇囟鹊募眲≡黾佣鵁龤?�。這時(shí)需要更換飽和電流更大的電感����。

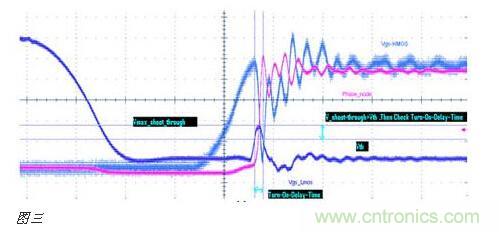

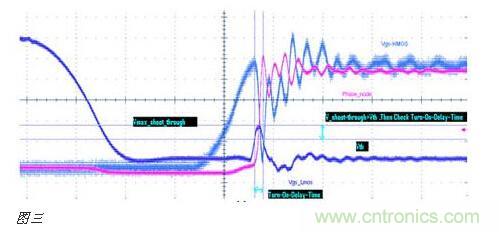

3.Shoot through測(cè)試

測(cè)試的目的是看上MOS管導(dǎo)通時(shí),有沒有同時(shí)把下管打開����,從而導(dǎo)致電源直接導(dǎo)通到地而引起短路。如圖三所示藍(lán)色曲線(Vgs_Lmos)就是下管在上管導(dǎo)通的同時(shí)���,被帶了起來���,如果藍(lán)色曲線的被帶起來的尖峰超過了MOS管的Vth要求,同時(shí)持續(xù)時(shí)間(Duration)也超過了datasheet要求���,從而就會(huì)有同時(shí)導(dǎo)通的風(fēng)險(xiǎn)�。當(dāng)然�,這是大家最常見到的情況。

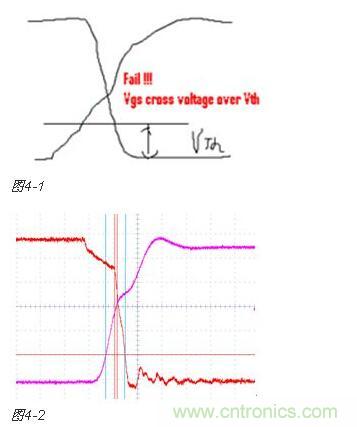

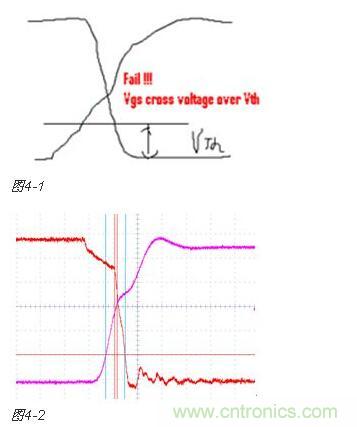

下面這種情況有非常多的人會(huì)忽視�,甚至是一些比較有經(jīng)驗(yàn)的電源測(cè)試工程師�����。下面組圖四是下管打開���,上管關(guān)閉時(shí)候的波形(圖4-1是示意圖,圖4-2示實(shí)際測(cè)試圖)���。雖然沒有被同時(shí)帶起的情況�,但是請(qǐng)注意上下管有交叉的現(xiàn)象����,而且交叉點(diǎn)的電平遠(yuǎn)高于MOS管規(guī)定的Vth值,這是個(gè)嚴(yán)重的shoot through現(xiàn)象�。最直接的后果就是MOS管燒毀!

[page]

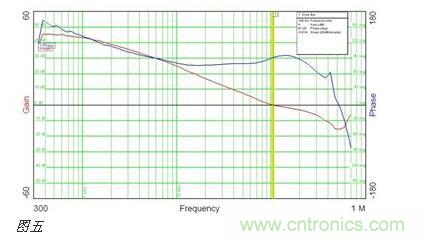

4.相位裕量和帶寬(phase margin and bandwidth)

相位裕量和帶寬是很多公司都沒有測(cè)試的項(xiàng)目(尤其是規(guī)模較小的公司受限于儀器)�����,但是這卻是個(gè)非常重要的測(cè)試項(xiàng)目��。電源系統(tǒng)是否穩(wěn)定�����,是否能長時(shí)間(3年或以上)有效工作���,相位裕量和帶寬可以在很大程度上說起了決定性的作用���。很多公司完全依賴于電源芯片廠家給的參考設(shè)計(jì)方案里的推薦值,但是跟你的設(shè)計(jì)往往有不小的差異�����,這樣會(huì)有很大的潛在風(fēng)險(xiǎn)���。

如果系統(tǒng)是一個(gè)不穩(wěn)定的系統(tǒng)����,反映在一些電源測(cè)試項(xiàng)目里面���,會(huì)看到以下幾個(gè)主要問題����。

電源的Noise測(cè)試通過�,但是電源依然不穩(wěn)定。表現(xiàn)為功能測(cè)試fail.常常有工程師在debug時(shí)說我的電源noise已經(jīng)很小了�����,加了很多電容了,為啥還是跑不動(dòng)呢����?其實(shí)是他的閉環(huán)系統(tǒng)本來就不穩(wěn)定。

Phase點(diǎn)jitter過大�。這是比較典型的不穩(wěn)定現(xiàn)象。

瞬態(tài)響應(yīng)太大���。最笨的辦法就是加很多電容��,去滿足瞬態(tài)響應(yīng)的要求���。對(duì)于低成本產(chǎn)品,這可是要錢的啊����。

如果你沒有用正確的方法測(cè)試出系統(tǒng)的環(huán)路增益的波特圖,那么你如何下手去調(diào)試這些項(xiàng)目讓他通過測(cè)試呢���?只有來來回回不停作實(shí)驗(yàn)�����。然后來來回回跑功能測(cè)試���。Oh,my god����,浩大的工作量。而且���,對(duì)于一些低成本的產(chǎn)品�,往往用到了鋁電解電容����,MLCC電容等低成本方案(電感,電阻值基本沒有變化)����。這些電容的容值會(huì)隨著時(shí)間變化而減少。如MLCC����,系統(tǒng)運(yùn)行在正常溫度兩年~三年,容值會(huì)變到原來的一半�����。而這一半電容的變化,會(huì)對(duì)系統(tǒng)的穩(wěn)定造成很大的影響���,這也是為什么很多低價(jià)的產(chǎn)品質(zhì)量不可靠的一個(gè)重要原因�����。那是不是說價(jià)格越高���,用越多的電容就越好呢,當(dāng)然不是�。這就是為啥要測(cè)試相位裕量的原因。你需要調(diào)試一組合理的值���,能夠同時(shí)覆蓋全電容以及半電容的要求���。這樣同樣能做到低價(jià)格高品質(zhì)。

根據(jù)奈奎斯特定理對(duì)系統(tǒng)穩(wěn)定性要求����,規(guī)范要求一個(gè)閉環(huán)系統(tǒng)的相位裕量最少為60度,45~60度可以考慮為最低限額要求。對(duì)于帶寬�,200~500K的開關(guān)電源的要求在10%~30%的開關(guān)頻率。從開關(guān)電源的穩(wěn)定性看帶寬越低�,電源越容易穩(wěn)定。從開關(guān)電源的動(dòng)態(tài)指標(biāo)看��,帶寬越高電源的動(dòng)態(tài)性能越好�。

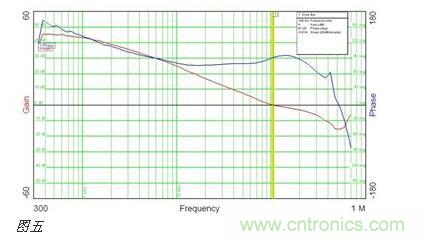

下圖五為典型的波特圖:

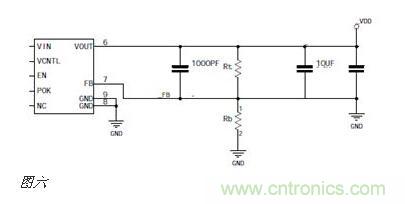

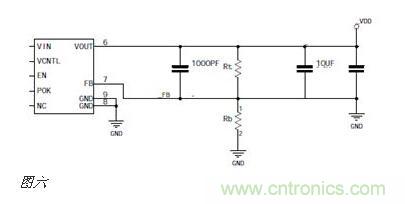

另外一點(diǎn)非常重要的是,除了PWM開關(guān)電源����,有很多線性電源(LDO)�����,其補(bǔ)償網(wǎng)絡(luò)在芯片外部的�����,也要做類似的環(huán)路增益的波特圖測(cè)試���,從而確保其穩(wěn)定性�����。LDO的測(cè)試�,是絕大多數(shù)廠家容易忽略掉的。比如如下圖六所示這種電路�����,很多人會(huì)直接測(cè)量噪聲完事����。

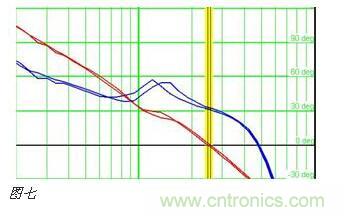

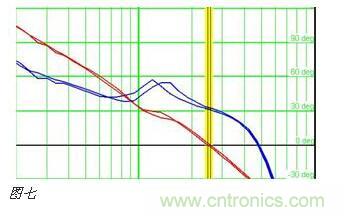

我們有可能會(huì)看到的相位裕量不能達(dá)到要求。如下圖七�,只有30度左右。這個(gè)時(shí)候�,只有調(diào)試不同的參數(shù),才能得到比較好的結(jié)果���。從而滿足系統(tǒng)穩(wěn)定性的要求��。

5.電源紋波和噪聲

電源紋波和噪聲���,看起來是電源測(cè)試?yán)锩孀詈唵蔚捻?xiàng)目。但是也有可能對(duì)你的測(cè)試結(jié)果和功能有比較大的影響�。

首先是紋波,我們測(cè)試的時(shí)候�����,只是看是不是符合規(guī)范要求,比如30mV等等�����。有些時(shí)候�,紋波和系統(tǒng)的PLL是有關(guān)系的。如果你的PLL jitter不過�����,可以考慮進(jìn)一步減小ripple.

噪聲��,有人會(huì)問����,為啥我的系統(tǒng)噪聲和他的系統(tǒng)噪聲基本是一個(gè)范圍����,但是我的系統(tǒng)會(huì)跑fail呢?首先我們要排除前面講的系統(tǒng)穩(wěn)定性原因����,然后,親,你有沒有用示波器做過FFT�,看看同樣噪聲在頻域上的區(qū)別呢?

小編推薦閱讀:

我愛快包——電子工程師的外快錢包