【導(dǎo)讀】隨著汽車工業(yè)的不斷發(fā)展其電氣化程度越來越深,從而其各種前/后裝設(shè)備的電氣系統(tǒng)穩(wěn)定性對車輛安全而言也愈加重要。例如根據(jù)GB/T 19056-2012和JT-T794-2011標(biāo)準(zhǔn),車載MDVR等產(chǎn)品就需強制通過電火花干擾測試以確保其穩(wěn)定可靠工作。

而與此同時,在目前MDVR智能化的趨勢下(AI),需要更精確的攝像頭視頻數(shù)據(jù)用于AI分析。此時用TI的FPDLINK-III來實現(xiàn)數(shù)字視頻信號的傳輸,相較傳統(tǒng)的模擬視頻信號傳輸優(yōu)勢明顯,但挑戰(zhàn)的是:在上述電火花干擾測試方面,F(xiàn)PDLINK更高頻的信號傳輸也更易受到干擾,本文即主要針對該問題進(jìn)行原理剖析,并整理相應(yīng)優(yōu)化方法以應(yīng)對該挑戰(zhàn)。

1. 實驗?zāi)P图案蓴_途徑

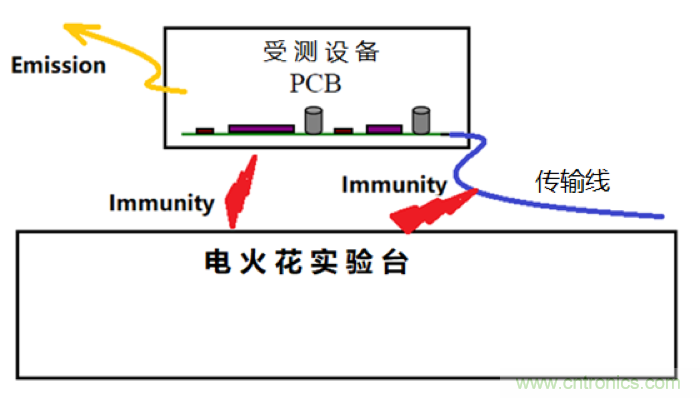

電火花干擾實驗?zāi)P涂蓞⒖枷聢Dfig.1,同時實驗用電火花信號規(guī)格如table.1。

Fig.1 電火花干擾實驗?zāi)P?/div>

Tabl.1 電火花信號規(guī)格

通過上圖我們可看出,電火花干擾實驗基本等效于存在外界強干擾源情況下的EMC抗擾測試(EMS),此時受測終端設(shè)備被電火花所激發(fā)電磁場通過輻射的方式所干擾,而主要傳遞途徑包含F(xiàn)PDLINK傳輸線以及受測設(shè)備PCB走線等,后續(xù)我們也就分別從這兩個方面來簡述其原理及優(yōu)化方式。

2. 干擾原理及優(yōu)化方式

a. PCB干擾

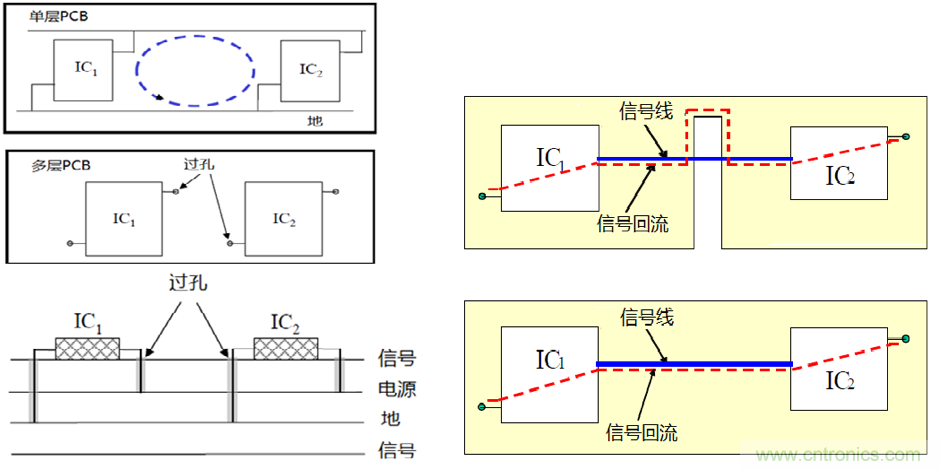

實驗臺中的電火花會激發(fā)強電磁場,此時受測設(shè)備也隨之處于一個很強的輻射環(huán)境下,而其中的PCB會從兩個方面被干擾并產(chǎn)生噪聲電壓/電流,從而影響系統(tǒng)正常工作:

一是PCB不同網(wǎng)絡(luò)/層間有寄生電容(網(wǎng)絡(luò)鋪銅面積越大寄生電容越大),此時會在該寄生電容上耦合產(chǎn)生電壓噪聲,從而影響系統(tǒng)正常工作。

另一是PCB上構(gòu)成回路的走線可等效看成感性線圈,在強磁場的影響下會耦合產(chǎn)生噪聲電流,通過板上阻抗最終也可轉(zhuǎn)化為噪聲電壓從而影響系統(tǒng)正常工作。

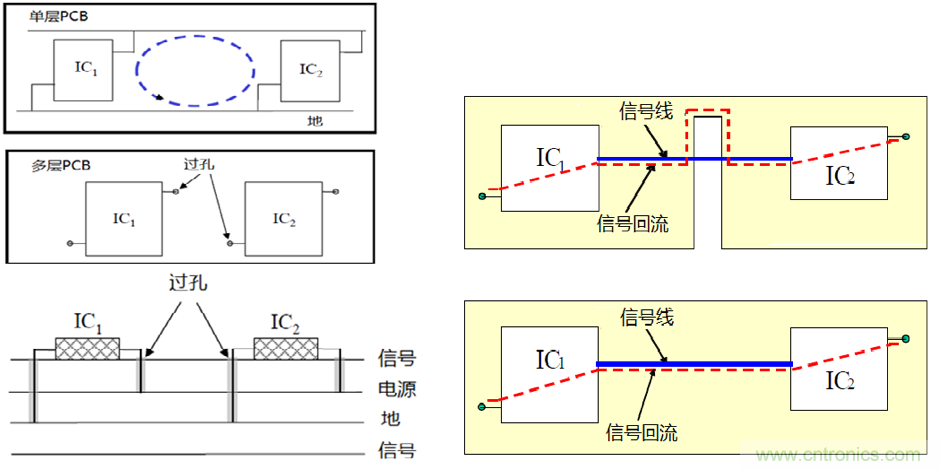

下圖模型可幫助進(jìn)一步理解上述兩種干擾形成的過程。

Fig.2 干擾耦合方式

基于以上原理,對于電火花干擾,在PCB上我們可做如下優(yōu)化來提升其抗擾能力:

● 盡量用多層板(單層板往往會導(dǎo)致各電源/信號至地的走線回路更大,從而產(chǎn)生如上更大的感性耦合干擾)

● 設(shè)置單獨的電源層和地層

● 多層板的板層間距盡量大些,從而減小寄生電容隨之減少如上的容性耦合干擾

● 高速信號線需避免回路中有空隙/阻斷等

Fig.3 PCB layout 建議

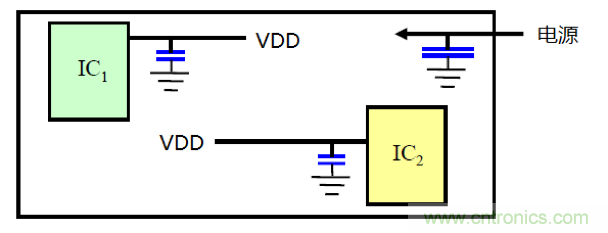

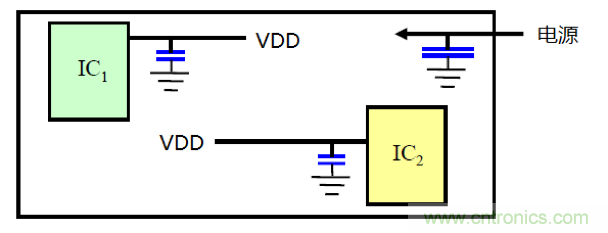

同時原理圖設(shè)計時,在各芯片VDD或其他管腳上放置單獨的退耦電容也是一個消除該干擾的常用方法。(信號管腳需留意退耦電容是否影響正常通信等)

Fig.4 退耦電容

最后,對于這種情況下PCB的輻射干擾,一個完全閉封的導(dǎo)電金屬外殼或板上屏蔽罩也有很好的優(yōu)化作用,但這種方式對產(chǎn)品成本影響較大,建議根據(jù)實際產(chǎn)品情況酌情考慮。

b. 傳輸線干擾

傳輸線干擾的模型比較簡單,此時可將傳輸線看作一根長的天線,在電火花實驗產(chǎn)生的射頻干擾環(huán)境下會直接產(chǎn)生噪聲從而影響正常視頻信號質(zhì)量。

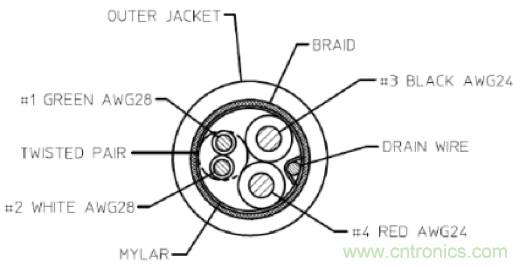

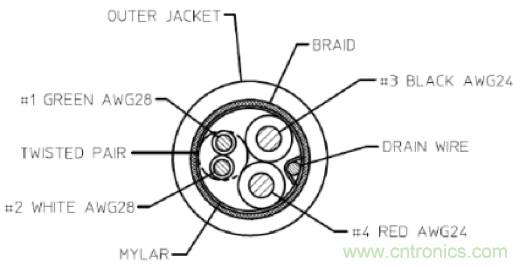

所以在傳輸線的干擾優(yōu)化上,一個良好的線纜屏蔽層就非常重要,推薦如下類型的STP與屏蔽同軸線。

fig.5 STP線

fig.6 屏蔽同軸線

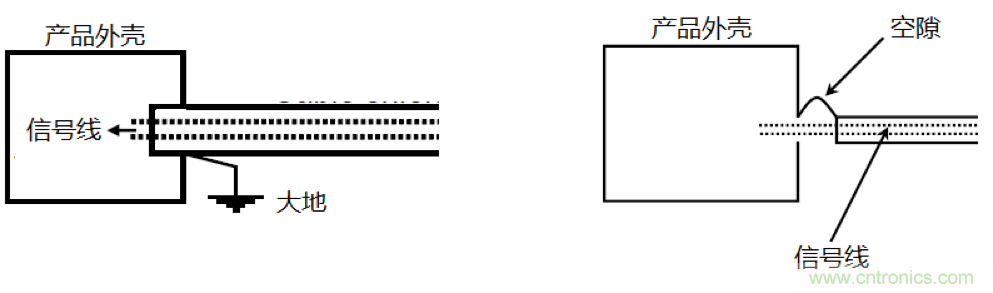

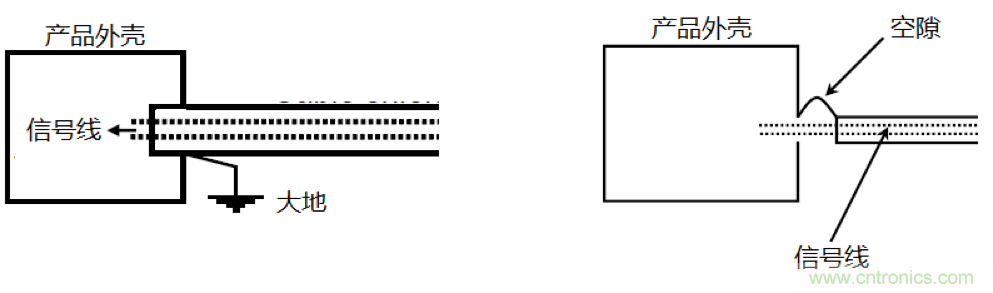

建議將屏蔽線接頭撥線部分延伸入金屬外殼內(nèi)部而不要暴露在外面,同時線纜屏蔽層接大地以為干擾信號提供良好的耗散回路。

fig.7 傳輸線連接處理

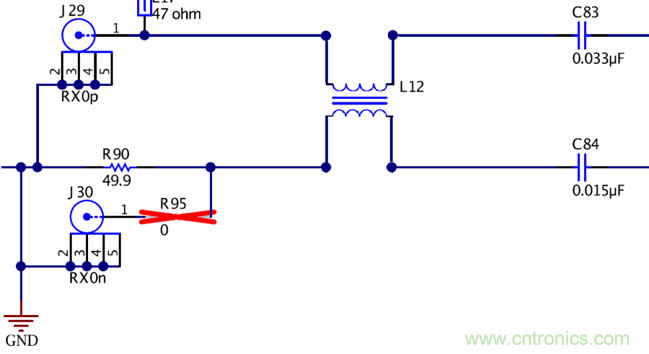

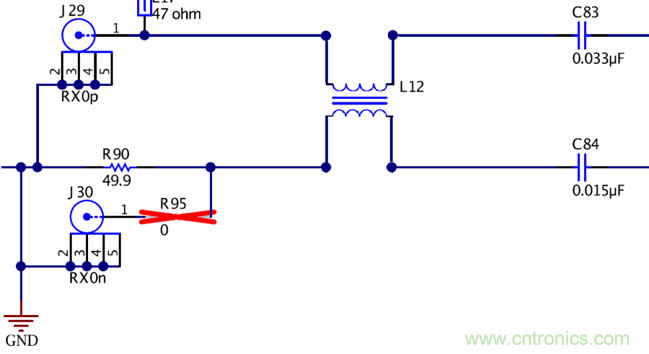

除了線纜屏蔽,另外一個可以對傳輸線干擾優(yōu)化的方式是,在線纜的輸入端放一個共模電感,可參照TI-FPDLINK芯片的參考設(shè)計(如下為DS90UB954 參考設(shè)計),這樣對已經(jīng)耦合進(jìn)傳輸線的噪聲也能起來一定濾除作用。

fig.8 FPDLINK輸入共模濾波

免責(zé)聲明:本文為轉(zhuǎn)載文章,轉(zhuǎn)載此文目的在于傳遞更多信息,版權(quán)歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權(quán)問題,請聯(lián)系小編進(jìn)行處理。

推薦閱讀: