【導(dǎo)讀】由于具有較低的偏置電流,人們經(jīng)常選用CMOS和JFET運(yùn)算放大器。然而你應(yīng)該意識(shí)到,這個(gè)事實(shí)還與很多其它的原因相關(guān)。

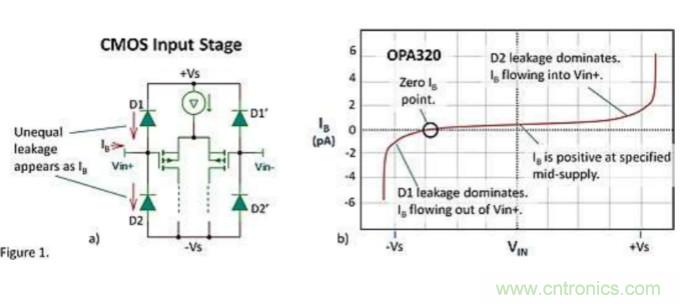

CMOS晶體管的柵極 (CMOS運(yùn)算放大器的輸入端)有極低的輸入電流。必須設(shè)計(jì)附加的電路來對脆弱的柵極進(jìn)行ESD和EOS保護(hù)。這些附加的電路是輸入偏置電流的主要來源。這些保護(hù)電路一般都通過在電源軌之間接入鉗位二極管來實(shí)現(xiàn)。圖1a中的OPA320就是一個(gè)例子。這些二極管會(huì)存在大約幾皮安的漏電流。當(dāng)輸入電壓大約達(dá)到電源軌中間值的時(shí)候,漏電流匹配的相當(dāng)好,僅僅會(huì)存在小于1皮安的殘余誤差電流而成為放大器輸入偏置電流。

當(dāng)輸入電壓接近電源電壓時(shí),兩個(gè)二極管泄漏電流間的關(guān)系會(huì)發(fā)生變化。輸入電壓靠近軌底的時(shí)候,舉例來講,當(dāng)D2的反相電壓接近零時(shí),其泄漏電流值會(huì)減小。D1的泄漏會(huì)使得輸入終端輸出更高的偏置電流。顯而易見,當(dāng)輸入電壓為正電源軌的時(shí)候,相反的情況會(huì)發(fā)生。輸入偏置電流值指的是在泄漏近乎匹配并且泄漏值極低的軌中間點(diǎn)測試所得到的值。

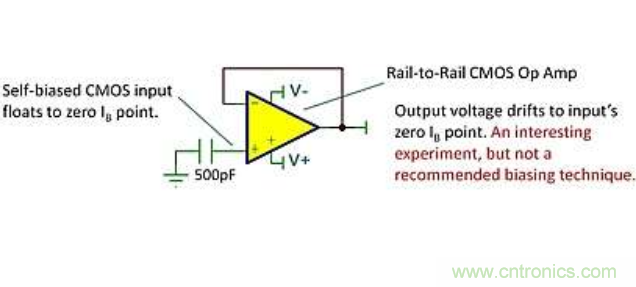

輸入電流和輸入電壓間的變化曲線如圖1b所示。對于任何給定的單元,都存在一個(gè)使輸入電流為零的輸入電壓(假設(shè)沒有顯著的封裝或者電路版圖的泄漏)。事實(shí)上,使用軌到軌運(yùn)算放大器時(shí),通常可以在輸入端使用自偏置(圖2),同時(shí)輸出將漂移到對應(yīng)零輸入偏置電流點(diǎn)的電壓。這是一個(gè)有趣的實(shí)驗(yàn),然而卻不是很實(shí)用。

JFET輸入的放大器有所不同,比如說OPA140。對OPA140來講,輸入晶體管的柵極是一個(gè)二極管結(jié),同時(shí)二極管結(jié)的泄漏電流常常是輸入偏置電流的主要來源。輸入二極管結(jié)通常會(huì)更大,因此會(huì)比保護(hù)二極管更容易泄漏。因此輸入偏置電流往往是不定向的。它會(huì)跟隨放大器變化。

由此可以得出結(jié)論。一定注意,如果極低偏置電流對電路非常重要,仔細(xì)查看性能圖表來收集所有可以得到的信息。如果在接近正電源軌或者負(fù)電源軌的情況下操作,你將會(huì)得到較高的輸入偏置電流。這將會(huì)引出另外一個(gè)重要的點(diǎn)-輸入偏置電流會(huì)隨著溫度的增加而顯著增加。在后邊的博客中會(huì)給出更多關(guān)于溫度效應(yīng)的討論。

本文適用于大多數(shù)通用的CMOS和JFET的放大器,然而還存在一些為極低輸入偏置電流而設(shè)計(jì)的專用放大器。他們使用創(chuàng)新的保護(hù)電路獨(dú)特的插腳引線來使IB在3fA的范圍之內(nèi),比通用放大器低三個(gè)數(shù)量級(jí)。比如說:

LMP7721-3fA輸入偏置電流的CMOS運(yùn)算放大器

INA116-極低輸入電流的儀表放大器

推薦閱讀: