【導(dǎo)讀】這種類型的AD轉(zhuǎn)換器可以獲得高分辨率,但是通常這樣做會犧牲速度。因此,這些轉(zhuǎn)換器不適用于音頻或信號處理的場合應(yīng)用。他們通常的典型應(yīng)用就是數(shù)字電壓計和其他需要高精度測量的儀表。

一個積分型ADC是一種通過使用積分器將未知的輸入電壓轉(zhuǎn)換成數(shù)字表示的一種模-數(shù)轉(zhuǎn)換器。在它最基本的實現(xiàn)中,這個未知的輸入電壓是被施加在積分器的輸入端,并且持續(xù)一個固定的時間段(所謂的上升階段)。然后用一個已知的反向電壓施加到積分器,這樣持續(xù)到積分器輸出歸零(所謂的下降階段)。這樣,輸入電壓的計算結(jié)果實際是參考電壓的一個函數(shù),定時上升階段時間和測得的下降階段時間。下降階段時間的測量通常是以轉(zhuǎn)換器的時鐘為單位,所以積分時間越長,分辨率越高。同樣的,轉(zhuǎn)換器的速度可以靠犧牲分辨率來獲得提升。

這種類型的AD轉(zhuǎn)換器可以獲得高分辨率,但是通常這樣做會犧牲速度。因此,這些轉(zhuǎn)換器不適用于音頻或信號處理的場合應(yīng)用。他們通常的典型應(yīng)用就是數(shù)字電壓計和其他需要高精度測量的儀表。

========基本設(shè)計=======

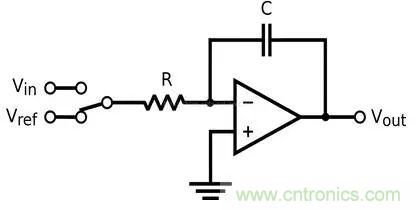

最基本的積分型ADC電路包含:

● 一個積分器、

● 一個選擇開關(guān)(用來選在被測電壓和參考電壓)、

● 一個定時器(用來決定對被測電壓的積分時間長度和測量參考電壓積分消耗時間)、

● 一個比較器(用來進行過零檢測)、

● 一個控制器、

● 一個放電開關(guān)(這個根據(jù)實現(xiàn)形式可有可無,主要用來對積分電容進行放電,與積分電容并聯(lián))。

上面的所有開關(guān)都由轉(zhuǎn)換器的控制器(通常是微處理器或?qū)S玫目刂七壿?,控制器的輸入包括一個時鐘信號(用來測量時間)和一個比較器的輸出信號(用來檢測積分器的輸出是否歸零)

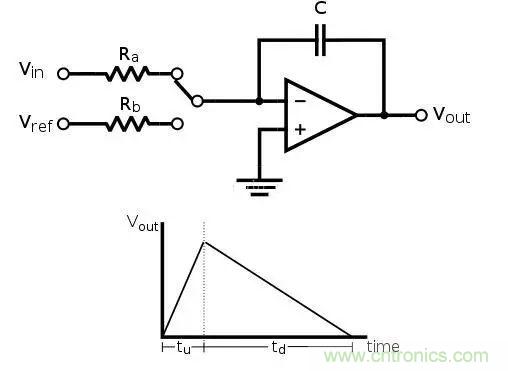

轉(zhuǎn)換過程分兩個階段:上升階段和下降階段。在上升階段,積分器的輸入是被測電壓,在下降階段,積分器的輸入是已知的參考電壓。在上升階段中,開關(guān)選擇被測電壓進入積分器,積分器持續(xù)一個固定的時間段進行積分,在積分電容上面積累電荷。在下降階段,開關(guān)選擇參考電壓進入積分器,在這階段測量積分器輸入歸零的時間。(譯者:總結(jié)起來就是先定時積分,再定值反向積分,測量反向積分時間),電路如右圖:

為了使積分器向相反方向積分,參考電壓需要和被測電壓的極性相反。在大多數(shù)情況下,如果被測電壓為正,那么參考電壓就為負。為了能夠處理正負電壓輸入的情況,需要一個正向和一個負向的參考電壓。具體選擇哪一個參考電壓取決于上升階段積分結(jié)束后積分器的輸出電壓極性。也就是說,如果在上升階段結(jié)束時,積分器輸出是負,則需要接入一個負向參考電壓(譯者:因為接的是積分器的反向輸入端),如果積分器輸出是正,則需要接入一個正向參考電壓。

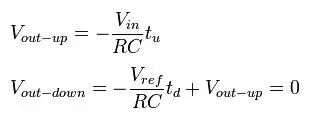

積分器輸出的基本公式如下(假設(shè)是一個恒定輸入):

假設(shè)在每個轉(zhuǎn)換過程的初始電壓都是零,并且積分器在下降階段結(jié)束時的輸出電壓也是零,我們就可以得到下面兩個等式來表示積分器的兩個階段的輸出:

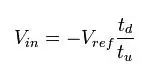

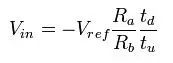

結(jié)合上面兩個等式,可以解除Vin,也就是得到了被測電壓的公式:

從這個公式可以看出,雙斜坡積分ADC的好處之一很明顯:測量結(jié)果與電路元件的值(其中的R和C)無關(guān)。然而,這并不意味著,R和C在雙斜坡積分ADC中不重要(下面將解釋這一問題)。

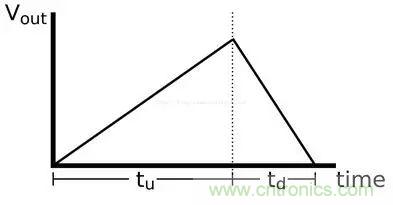

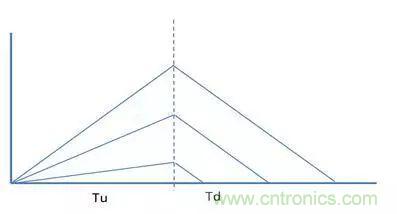

注意到在下圖中,在上升階段電壓是向上升高的,在下降階段電壓是向下降低的。在實際應(yīng)用中,由于比較器使用的是運放的負反饋,施加一個正向電壓Vin實際會使輸出下降,

所以這里的“上”和“下”可以理解為積分電容充電的過程。

雙斜坡積分型ADC的分辨率主要由下降階段的時間長度和時間測量分辨率(例如控制器時鐘的頻率)來決定的(譯者:也就是速度和分辨率這一對矛盾的原因)。期望的分辨率(用bits數(shù)表示) 是滿量程輸入時,下降時間的最小長度。(Vin = -Vref)

在滿程輸入的測量過程中,積分器輸出的斜坡在上升和下降階段是相同的(方向相反)。也就是上升和下降階段的時間相等( ),總的測量時間則為

),總的測量時間則為

<img%20border="1"%20alt=""%20src="http: 2="" img.blog.csdn.net="" watermark="" text="" ahr0cdovl2jsb2cuy3nkbi5uzxqvexbvzmx5zxi="/font/5a6L5L2T/fontsize/400/fill/I0JBQkFCMA==/dissolve/70/gravity/Center"%20width="25"%20height="17"%20/"></img%20border="1"%20alt=""%20src="http:>

。因此,滿程輸入的總的測量時間是基于期望的分辨率和控制器的時鐘頻率的。

如下式:

舉個栗子:如果期望得到16bits的分辨率,控制器時鐘頻率是10MHz,那么測量時間計算下來就是13.1ms(也即是每秒鐘76個采樣)。采樣時間可以靠犧牲分辨率得到改善。如果分辨率降低到10bits,那么在同樣的10MHz的時鐘頻率下,測量時間就降低到僅為0.2ms(每秒鐘4900個采樣)。

========局限性=======

雙斜坡積分型ADC有幾個局限。對于基本的雙斜坡ADC來說,靠使用更長的測量時間或更高的時鐘頻率來任意提高分辨率是不可能的。分辨率被以下條件所限制:

1. 積分器運放的范圍。運放的軌電壓限制了積分器的輸出電壓。長時間的積分器輸入會導(dǎo)致輸出被限制到一個最大值,是的任何基于下降時間的計算都沒有意義。因此,應(yīng)基于運放的軌電壓、參考電壓和期望的滿程被測電壓來小心地選擇積分器的電阻和電容,并且最長的上升時間也應(yīng)滿足期望的分辨率。(譯者:實際就是講積分器飽和的問題,后面的電荷平衡技術(shù)將解決這個問題)

2. 作為過零檢測的比較器的準確度。寬帶電路噪聲限值了比較器精確檢測積分器輸出歸零的能力。Goerke建議一個典型的限制是比較器分辨率1mV。

3. 積分電容的品質(zhì)。盡管積分電容不需要完美的線性,但卻需要時間恒定(time-invariant)。介電吸收(Dielectric absorption)會導(dǎo)致嚴重問題。(譯者:個人認為此處應(yīng)為介質(zhì)吸收。取一個數(shù)值較大的鉭電容,充電到10V左右,用一個100Ω的電阻即刻跨接在它兩端,迅速放電。移去電阻,用高阻抗的電壓表觀察電容兩端的電壓,可以看到電容又充電,幾秒后達到1V左右。介質(zhì)吸收現(xiàn)象可能與介質(zhì)表面的殘留極化有關(guān)。所以積分型ADC的電容應(yīng)選擇高質(zhì)量、低介質(zhì)吸收的電容,如特氟龍介質(zhì))

========改善=======

基本雙斜坡積分型ADC的設(shè)計在轉(zhuǎn)換速度和分辨率方面有限制。很對針對基本設(shè)計的修改在某種程度上解決了這些問題。

針對上升階段的改進

改進的雙斜坡

基本雙斜坡設(shè)計的上升階段會將被測電壓固定積分一段時間。也就是說,它最終會在積分電容上建立一個不確定的電荷量。下降階段測量這個不確定的電荷來確定被測電壓。對于一個滿程輸入,測量時間的一半會被花費到上升階段。對于更小的輸入,相對總測量時間的一個更大比例的時間會被花費到上升階段。所以,減少花費到上升階段的時間可以顯著降低總的測量時間。(譯者:此處以圖示似乎更容易說明問題。見下圖)

一個簡單的減少上升時間的方法就是增加充電電荷的積累速度,這可以靠減少輸入電阻值來實現(xiàn)。這依然是要積累同等數(shù)量的電荷,只是需要的時間更少。在下降階段使用同樣的算法,參考右圖,則得到下面的公式:

與基本雙斜坡積分轉(zhuǎn)換器不同,此等式與積分電阻有關(guān)。或者,更重要的是,它與兩個積分電阻的比值有關(guān)。這種改進方法不能改進轉(zhuǎn)換器的分辨率(因為它沒有解決上面提到的分辨率的限值)。

推薦閱讀: