【導(dǎo)讀】鎖相環(huán) (PLL) 是現(xiàn)代通信系統(tǒng)的基本組成部分。PLL 通常用于在接收器和發(fā)送器中提供本機(jī)振蕩器; (LO) 功能��;此外���,它們還用于時(shí)鐘信號(hào)分布和降噪—,并且越來越多地用作高采樣率模數(shù) (A/D) 轉(zhuǎn)換的時(shí)鐘源���。

隨著特征尺寸在集成電路工藝中不斷縮小�,器件電源電壓(包括 PLL 和其他混合信號(hào)功能的電源)也呈現(xiàn)出下降趨勢(shì)��。然而��,作為 PLL 的關(guān)鍵元件�,壓控振蕩器 (VCO) 的實(shí)用技術(shù)的使用并沒有以同樣快的速度下行。許多高性能 VCO 設(shè)計(jì)仍然采用可能需要高達(dá) 30 V 電源電壓的離散電路來實(shí)現(xiàn)����。這給當(dāng)今的 PLL 或 RF 系統(tǒng)設(shè)計(jì)師帶來了嚴(yán)峻的挑戰(zhàn):’將低電壓 PLL IC 與更高電壓的 VCO 連接在一起。電平轉(zhuǎn)換接口通常采用有源濾波電路加以實(shí)現(xiàn) — 稍后討論���。

本文將介紹 PLL 的基本知識(shí)�,探討具有高電壓 VCO 的 PLL 設(shè)計(jì)的當(dāng)前發(fā)展水平��,討論典型架構(gòu)的利弊,并介紹高電壓 VCO 的一些替代選項(xiàng)����。

PLL 基本知識(shí)

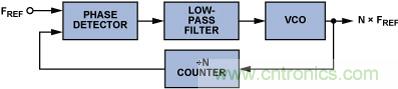

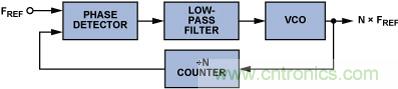

鎖相環(huán)(圖 1)是一個(gè)反饋系統(tǒng),在其中��,相位比較器或檢測(cè)器驅(qū)動(dòng)反饋環(huán)路中的 VCO��,使振蕩器頻率(或相位)精確地跟蹤所應(yīng)用的基準(zhǔn)頻率��。通常需要濾波電路以集成和平整正負(fù)誤差信號(hào)—�����,并提升環(huán)路穩(wěn)定性�。分頻器通常包含在反饋路徑中�,以在 VCO 的范圍內(nèi)將輸出頻率確定為基準(zhǔn)頻率的倍數(shù)。分頻器可以根據(jù)需要進(jìn)行實(shí)現(xiàn)���,以使頻率倍數(shù) N 為整數(shù)或小數(shù)���,因此 PLL 被劃分為整數(shù) N PLL 或小數(shù) N PLL。

圖 1. 基本鎖相環(huán)���。

由于 PLL 是一個(gè)負(fù)反饋控制環(huán)路���,因此頻率誤差信號(hào)將在平衡點(diǎn)被強(qiáng)制歸零�����,從而在 VCO 輸出處產(chǎn)生準(zhǔn)確且穩(wěn)定的 N × FREF 頻率���。

PLL 可以采用純數(shù)字、純模擬或組合電路以各種方式實(shí)現(xiàn)����,具體取決于所要求的頻率范圍、噪聲��、雜散性能以及物理尺寸�����。目前��,通過選擇適用于高頻或射頻的架構(gòu)���,PLL 將純數(shù)字組件(例如反饋分頻器和相位檢測(cè)器)與高精度的模擬電路(例如電荷泵和 VCO)組合在一起���?�;旌闲盘?hào) PLL 的主要組件包括:

1. 基準(zhǔn)頻率:射頻輸出將相位鎖定至的穩(wěn)定且準(zhǔn)確的基準(zhǔn)頻率�。它通常來自晶體或溫控晶體振蕩器 (TCXO)�����。

2. 相位頻率檢測(cè)器 (PFD):從參考信號(hào)和反饋信號(hào)中提取相位誤差信號(hào)���。

3. 電荷泵:將誤差信號(hào)轉(zhuǎn)換成與相位誤差成正比的正或負(fù)電流脈沖串�。

4. 環(huán)路濾波器:整合來自電荷泵的電流脈沖��,從而為 VCO 調(diào)諧端口提供純凈的電壓��。

5. VCO:根據(jù)提供給其調(diào)諧端口的電壓 (Vtune) 來輸出頻率��。VCO 具有增益�,KV���,單位為 MHz/V��。表示輸出頻率和輸入控制電壓之間關(guān)系的基本 VCO 表達(dá)式為 fo = fc + Kv (Vtune)����,其中 fc 是 VCO 偏置頻率。

6. N 分頻器:分解輸出頻率以等于 PFD 或基準(zhǔn)頻率�。它可以直接除以一個(gè)整數(shù) — 或者在更多的情況下,它被實(shí)現(xiàn)成小數(shù)分頻器��。小數(shù)分頻器可通過以下方法輕松實(shí)現(xiàn):切換整數(shù)分頻器中的分值以得到小數(shù)平均值(例如�,要得到平均值 4.25,可以計(jì)數(shù)到 4 三次��,并計(jì)數(shù)到 5 一次�。一共計(jì)算 17 個(gè)脈沖,并且創(chuàng)建了 4 個(gè)脈沖����;因此頻率比為 17/4 = 4.25)。在實(shí)踐中���,可以通過借用高分辨率噪聲形狀轉(zhuǎn)換器中使用的技術(shù)來獲得更好的結(jié)果����。因此���,小數(shù)引擎通常使用可減少雜散頻率的 Σ-Δ 架構(gòu)來實(shí)現(xiàn)�����。

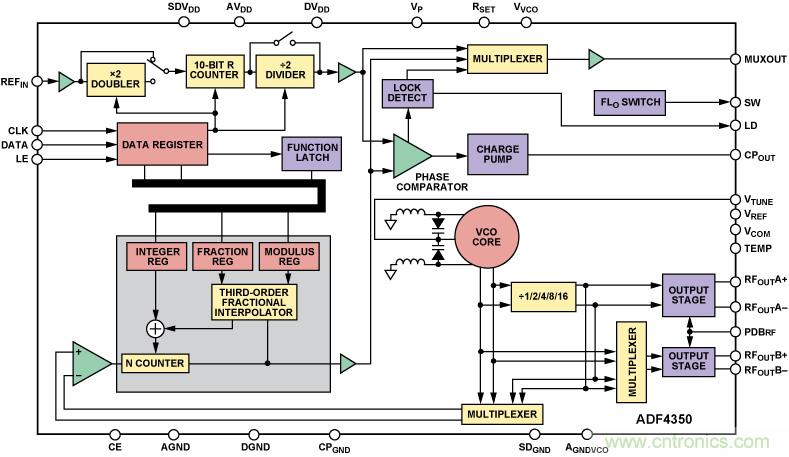

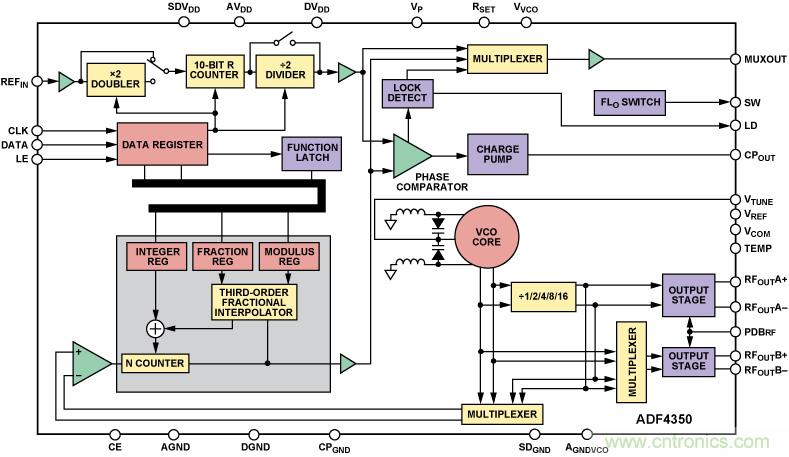

作為現(xiàn)有設(shè)備中使用的高度集成電路的一個(gè)示例����,圖 2 顯示了小數(shù) N PLL IC(帶有集成 VCO 的 ADF4350 寬帶頻率合成器)的結(jié)構(gòu)框圖;它的輸出頻率范圍為 137.5 MHz 至 4400 MHz�。(有關(guān)其功能的簡(jiǎn)要概述,請(qǐng)參閱帶有集成 VCO 的寬帶 PLL 部分���。)

圖 2. ADF4350 PLL 頻率合成器結(jié)構(gòu)框圖���。

PLL 的主要性能限制特性是相位噪聲、雜散頻率和鎖定時(shí)間��。

相位噪聲:相位噪聲是在頻域中評(píng)估的振蕩器或 PLL 噪聲�����,相當(dāng)于時(shí)域中的抖動(dòng)��。它是 PLL 中各種組件產(chǎn)生的噪聲的有效值總和�?���;陔姾杀玫?PLL 將在環(huán)路濾波器寬帶內(nèi)部抑制 VCO 噪聲��。在環(huán)路寬帶之外�����,VCO 噪聲占主導(dǎo)地位��。

雜散頻率:雜散頻率分量是由電荷泵定期更新 VCO 調(diào)頻電壓造成的�。它們將出現(xiàn)在由 PFD 頻率生成的載波的頻率偏置處�。在小數(shù) N PLL 中,還會(huì)在小數(shù)分頻器的作用下產(chǎn)生雜散���。

鎖定時(shí)間:當(dāng)從一個(gè)頻率變化到另一個(gè)頻率或響應(yīng)一個(gè)短暫的偏置時(shí)�����,PLL 的相位或頻率返回到鎖定范圍所用的時(shí)間��。它可以按照頻率或相位的調(diào)整情況加以指定�����。它作為一個(gè)規(guī)格的重要程度取決于應(yīng)用場(chǎng)合�����。

VCO 為何仍使用高電壓�?

高性能 VCO 是目前剩余的、抵御硅集成浪潮的最后電子元件之一���。僅在過去數(shù)年里�,用于蜂窩手機(jī)的 VCO 已完全集成到其無線芯片組中�����。然而���,蜂窩基站����、微波點(diǎn)對(duì)點(diǎn)系統(tǒng)����、軍事和航空航天以及其他高性能應(yīng)用領(lǐng)域仍在拓展硅基 VCO 的功能,并且仍然采用離散的方法實(shí)現(xiàn)�����。下面列出了原因:

大多數(shù)市售的離散 VCO 使用可變電容的變?nèi)荻O管作為基于 LC 的諧振電路中的調(diào)諧元件����。改變二極管的電壓可以更改其電容,進(jìn)而可以更改諧振電路的諧振頻率����。

變?nèi)荻O管上的任何電壓噪聲都會(huì)由 VCO 增益 KV(單位為 MHz/V)放大,并轉(zhuǎn)換為相位噪聲�。為了將 VCO 相位噪聲減至最低,KV 必須盡可能地低���,然而�����,實(shí)現(xiàn)合理寬度的調(diào)諧范圍需要較大的 KV�����。因此����,對(duì)于既需要低相位噪聲,又需要寬調(diào)諧范圍的應(yīng)用場(chǎng)合�,VCO 制造商通常設(shè)計(jì)具有低增益和較大輸入電壓范圍的振蕩器,以滿足這些相互矛盾的要求���。

對(duì)于窄帶 VCO 來說��,典型的電壓調(diào)諧范圍為 0.5 V 至 4.5 V�����,而寬帶 VCO 的典型電壓調(diào)諧范圍為 1 V 至 14 V��,在某些情況下�,調(diào)諧范圍甚至寬達(dá) 1 V 至 28 V���。

同軸諧振器振蕩器 (CRO) 是另一種特殊類型的 VCO���,使用非常低的增益和較寬的輸入調(diào)諧電壓來實(shí)現(xiàn)超低的相位噪聲性能。 它們通常用于窄帶專用移動(dòng)無線通信和陸上移動(dòng)無線通信應(yīng)用領(lǐng)域��。

連接到高壓 VCO

大多數(shù)商業(yè) PLL 頻率合成器 IC 具有最大可提供約 5.5 V 電壓的電荷泵輸出��,不足以直接驅(qū)動(dòng)需要更高調(diào)諧電壓的 VCO(如果環(huán)路濾波器僅使用無源元件)���。為了達(dá)到更高的調(diào)諧電壓�,必須采用一種運(yùn)用運(yùn)算放大器電路的有源環(huán)路濾波器拓?fù)浣Y(jié)構(gòu)。

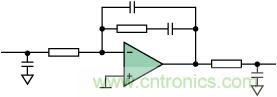

要實(shí)現(xiàn)這一目的�,最簡(jiǎn)單方法是在無源環(huán)路濾波器之后添加一個(gè)增益級(jí)�����。雖然設(shè)計(jì)簡(jiǎn)單�����,但這種方法存在一些隱患:反相運(yùn)算放大器配置提供的低輸入阻抗會(huì)加載無源環(huán)路濾波器�,改變了環(huán)路動(dòng)態(tài);同相配置可以提供足夠高的輸入阻抗�����,不會(huì)加載濾波器�,但有源濾波器增益會(huì)放大任何運(yùn)算放大器的噪聲,并且得不到前面無源環(huán)路濾波器提供的濾波好處�����。一種更好的拓?fù)浣Y(jié)構(gòu)是將增益級(jí)和濾波器集成到單個(gè)有源濾波器組件中��。建議進(jìn)行預(yù)濾波,以免來自電荷泵的極短電流脈沖過度驅(qū)動(dòng)放大器—���,這可能會(huì)限制輸入電壓的大小����。

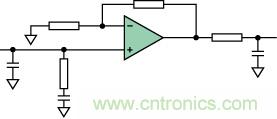

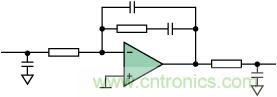

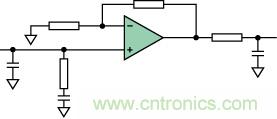

圖 3 顯示了兩個(gè)推薦的有源濾波器拓?fù)浣Y(jié)構(gòu)示例����,它們采用反相和同相增益進(jìn)行了預(yù)濾波。請(qǐng)注意����,這些放大器電路是真正的時(shí)間積分器,它們會(huì)強(qiáng)制 PLL 的環(huán)路在它們的輸入處保持零誤差����。在環(huán)路之外,所示的拓?fù)浣Y(jié)構(gòu)可能漂移到供電軌����。

a. 反相拓?fù)浣Y(jié)構(gòu)。

b. 同相拓?fù)浣Y(jié)構(gòu)�。

圖 3. 使用預(yù)濾波的有源濾波器。

反相拓?fù)浣Y(jié)構(gòu)具有在固定電壓下偏置電荷泵的優(yōu)勢(shì)����,通?�?梢赃_(dá)到電荷泵電壓的一半 (VP/2)—����,因此可以實(shí)現(xiàn)最佳的雜散性能�。注意要提供純凈的偏置電壓�����,最好來自專用的低噪聲線性穩(wěn)壓器����,例如 ADP150,并且盡可能靠近運(yùn)算放大器輸入引腳進(jìn)行充分解耦�。分頻器網(wǎng)絡(luò)中使用的電阻值應(yīng)盡量小,以減少它們產(chǎn)生的噪聲���。當(dāng)使用反相拓?fù)浣Y(jié)構(gòu)時(shí)���,關(guān)鍵是要確保 PLL IC 允許 PFD 極性反轉(zhuǎn),如有必要���,取消運(yùn)算放大器的反向并以正確的極性驅(qū)動(dòng) VCO����。ADF4xxx 系列具有這一特性。

同相環(huán)路濾波器配置不需要進(jìn)行專門的偏置���,因此可以提供更緊湊的解決方案���。電荷泵電壓不會(huì)在一個(gè)固定水平下偏置,并且現(xiàn)在可在其整個(gè)操作范圍內(nèi)變化��。因此�,在使用此濾波器類型時(shí),更為重要的是使用一個(gè)具有軌到軌輸入的運(yùn)算放大器����。(下一節(jié)將介紹輸入電壓范圍要求。)

選擇運(yùn)算放大器

選擇運(yùn)算放大器是讓有源濾波器發(fā)揮最佳性能的關(guān)鍵�����。除了帶寬外�,要考慮的主要性能規(guī)格還包括:

● 噪聲電壓密度—單位為 nV/√Hz

● 電流噪聲—單位為 pA/√Hz

● 輸入偏置電流

● 共模電壓范圍

濾波器的輸出直接影響產(chǎn)生的頻率和相位;因此��,運(yùn)算放大器的噪聲電壓密度指示了有源濾波器所添加的相位噪聲量。放大器噪聲不僅添加到 PLL 環(huán)路帶寬中���,而且還添加到帶外 — 并在環(huán)路濾波器的轉(zhuǎn)折頻率處最為明顯��,對(duì)于具有高噪聲電壓密度的放大器而言�,更是如此���。因此���,關(guān)鍵是要保持較低的放大器噪聲�,從而履行放大器和高電壓 VCO 的使命:提供更低的相位噪聲。一個(gè)不錯(cuò)的設(shè)計(jì)目標(biāo)是 <10 nV/√Hz��。與誤差電流脈沖相比���,電流噪聲通常小得多��,因此它的影響遠(yuǎn)遠(yuǎn)小于電壓噪聲的影響����。

如果運(yùn)算放大器的輸入偏置電流相對(duì)于 PFD 輸出電流明顯偏大���,則會(huì)在 PLL 輸出頻譜上產(chǎn)生較大的雜散頻率���。為了保持 VCO 調(diào)諧電壓始終相同和 PLL 鎖定��,電荷泵必須取代運(yùn)算放大器輸入在每個(gè) PFD 周期上吸取的偏置電流�。這將調(diào)整 PFD 頻率處的 VTUNE 電壓��,并導(dǎo)致載波周圍偏置處的雜散頻率等于 PFD 頻率���。輸入偏置電流越高����,VTUNE 電壓的調(diào)整越大�,并且雜散幅度越高。

共模電壓范圍或輸入電壓范圍 (IVR) 是另一個(gè)重要的運(yùn)算放大器規(guī)格�����,它常常被人忽略����,進(jìn)而導(dǎo)致最終設(shè)計(jì)出現(xiàn)嚴(yán)重問題。IVR 決定在輸入端子處最大/最小信號(hào)和正/負(fù)供電軌之間所需的間隙。

采用 ±15 V 的早期運(yùn)算放大器通常具有 ±12 V 的 IVR���。后來添加的緩慢橫向 PNP 輸入級(jí)允許 IVR 包括負(fù)供電軌�����,從而提供單電源能力����。盡管任何運(yùn)算放大器都將使用接地和正極電源運(yùn)行��,但有必要觀察它與供電軌之間的距離�����。

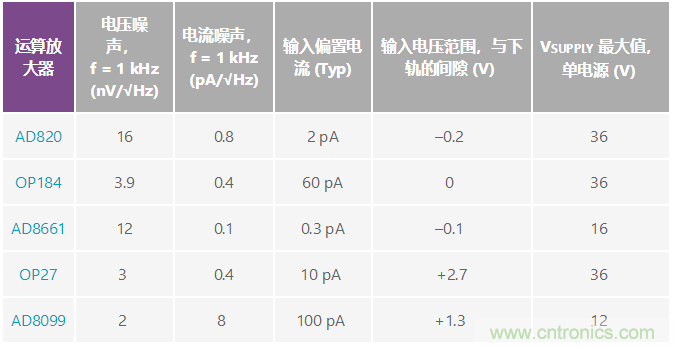

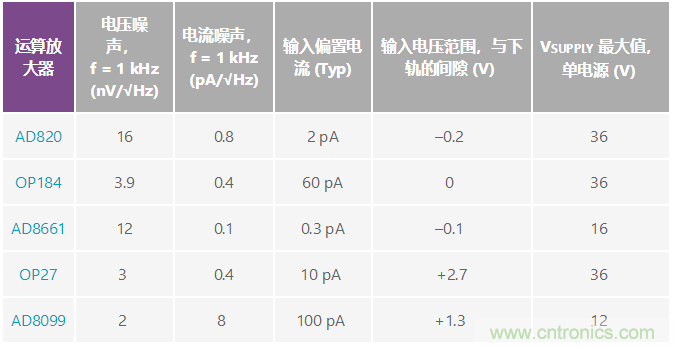

例如����,廣泛流行的 OP27 具有 ±12.3 V 的 IVR 以及 ±15 V 的電源��。這意味著輸入電壓至少需要與正���、負(fù)供電軌相距 ±2.7 V��。這種在范圍下端的限制使它不利于在單電源操作中使用寬輸入擺動(dòng)���。雙電源設(shè)計(jì)選項(xiàng)(如果有)允許更廣泛地選擇運(yùn)算放大器(并且簡(jiǎn)化了輸入偏置問題)���。如果需要單電源設(shè)計(jì),請(qǐng)使用允許輸入電壓從一個(gè)供電軌擺動(dòng)到另一個(gè)供電軌的運(yùn)算放大器(但其中的許多放大器可能具有更高的噪聲電壓規(guī)格)�。因此,為了獲得最佳結(jié)果��,需要符合以下條件的運(yùn)算放大器:具有低噪聲電壓密度���,以實(shí)現(xiàn)較低的相位噪聲��;具有較低的輸入偏置電流�����,以實(shí)現(xiàn)較低的雜散�;并且具有軌到軌輸入��,以實(shí)現(xiàn)單電源工作���。表 1 列出了一些模擬器件運(yùn)算放大器及其相對(duì)于上述設(shè)計(jì)標(biāo)準(zhǔn)的規(guī)格����。

表 1. 建議在 PLL 有源環(huán)路濾波器中使用的運(yùn)算放大器

運(yùn)算放大器的選擇取決于應(yīng)用場(chǎng)合。如果 PFD 雜散遠(yuǎn)離環(huán)路帶寬之外(例如在小數(shù)頻率合成器中)��,則適合使用雙極型晶體管輸入 (BJT) 運(yùn)算放大器 — 例如 OP184 或 OP27�����。BJT 的高輸入偏置電流所導(dǎo)致的 PFD 雜散將由環(huán)路濾波器進(jìn)行有效的衰減�����,并且 PLL 可以充分利用 BJT 運(yùn)算放大器的低噪聲電壓密度的優(yōu)勢(shì)��。

如果應(yīng)用場(chǎng)合需要較小的 PFD 與環(huán)路帶寬比率(例如��,在整數(shù) N 頻率合成器中)�,應(yīng)在噪聲和雜散水平之間達(dá)成妥協(xié);在此情況下��,AD820 和 AD8661 可能是不錯(cuò)的選擇���。

值得注意的是,雖然有源濾波器通常會(huì)增加 PLL 的噪聲���,但它們能充當(dāng)緩沖器����,這使它們?cè)谝恍?yīng)用細(xì)分領(lǐng)域能提供優(yōu)于無源濾波器的性能。例如����,如果 VCO 的調(diào)諧端口上具有會(huì)導(dǎo)致嚴(yán)重 PFD 雜散的高漏電流,可以使用運(yùn)算放大器來降低雜散水平�。運(yùn)算放大器的低阻抗輸出可以輕松供應(yīng)調(diào)諧端口漏電流。

設(shè)計(jì)示例

考慮一個(gè)示例���,在其中 LO 具有以下規(guī)格:

● 八倍頻調(diào)諧范圍為 1000 MHz 至 2000 MHz

● 相位噪聲要求為 –142 dBc/Hz(在 1 MHz 偏置處)

● 雜散 < –70 dBc

● 250-kHz 信道間距

● 鎖定時(shí)間 < 2 ms

● 提供 15 V 或 30 V 單電源

為了覆蓋 1 GHz 帶寬并滿足相位噪聲目標(biāo)�,需要使用高電壓 VCO 和有源環(huán)路濾波器���。相位噪聲和雜散規(guī)格以及單電源限制�����,將會(huì)驅(qū)動(dòng)運(yùn)算放大器的選擇��。為了滿足雜散規(guī)格���,運(yùn)算放大器輸入偏置電流必須較低��,而使用具有低電壓噪聲的運(yùn)算放大器可以實(shí)現(xiàn)最佳的相位噪聲�����。通過選擇 JFET-input 運(yùn)算放大器(例如輸入偏置電流為 0.3 pA 且電壓噪聲為 12 nV/√Hz 的 AD8661)��,可以在兩者之間達(dá)成完美妥協(xié)����。該器件還可以處理單電源要求���?����?蛇x擇 RFMD UMS-2000-A16 VCO 來覆蓋倍頻范圍�����。

最佳的入手點(diǎn)是一個(gè)涉及 ADIsimPLL™ 工具中支持的有源濾波器拓?fù)浣Y(jié)構(gòu)的模擬�。圖 3 中顯示了兩種推薦的濾波器類型����,但 ADIsimPLL 還支持其他配置。

對(duì)于 PLL����,選擇了可在整數(shù)或小數(shù)模式下工作的 ADF4150;它還提供了輸出分頻器選項(xiàng):2/4/8/16/32 — 允許連續(xù)覆蓋從 2 GHz 一直到 31.25 MHz 的頻率�。ADF4150 類似于圖 2 中顯示的 ADF4350,但它允許為那些需要滿足更嚴(yán)格相位噪聲要求的應(yīng)用場(chǎng)合選擇外部 VCO����。在模擬中,PLL 環(huán)路濾波器設(shè)置為 20 kHz���,以盡可能減少運(yùn)算放大器產(chǎn)生的噪聲���,同時(shí)保持 PLL 鎖定時(shí)間小于 2 ms。

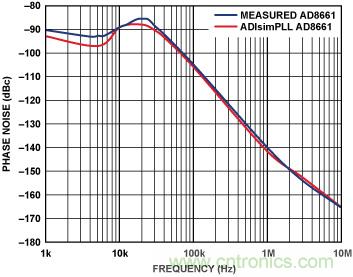

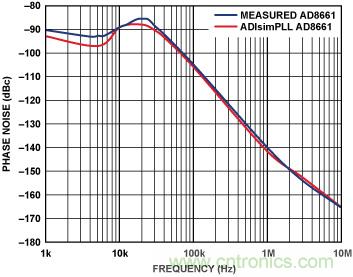

圖 4 將噪聲圖 (dBc) 顯示為模擬和測(cè)量系統(tǒng)(采用 ADF4150 PLL�、UMS VCO 和基于 AD8661 的濾波器)中頻率偏置的函數(shù)?���?稍趦蓚€(gè)噪聲配置文件中看到,由于有源環(huán)路濾波器增加了噪聲�,在 20 kHz 左右時(shí)最大達(dá)到 –90-dBc,但仍滿足 –142-dBc/Hz(1 MHz 偏置)的目標(biāo)�����。為了降低帶內(nèi)噪聲,可以以更高的雜散水平為代價(jià)使用更低噪聲的運(yùn)算放大器���,例如 OP184 或 OP27�;或?qū)?PLL 環(huán)路帶寬降低到 20 kHz 以下�。

圖 4. ADIsimPLL 模擬和測(cè)得的性能(在 PLL 有源濾波器中采用 AD8661 作為運(yùn)算放大器)。

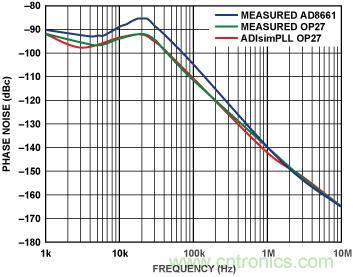

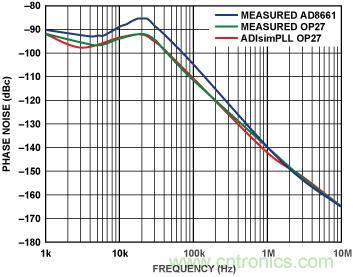

圖 5 顯示了在使用 OP27 時(shí)噪聲水平大約改善了 6 dB����。在此情況下,由于環(huán)路帶寬相對(duì)較窄���,雜散水平未顯著增加��。進(jìn)一步降低帶寬將改善偏置量低于100 kHz 時(shí)的相位噪聲�,為之付出的代價(jià)是 PLL 鎖定時(shí)間增加�。所有這些取舍均可以在進(jìn)入實(shí)驗(yàn)室之前使用 ADIsimPLL 模擬進(jìn)行測(cè)試。

圖 5. 在有源濾波器中采用 AD8661 和 OP27 時(shí)的 PLL 測(cè)量性能�。

重大新聞:高電壓 PLL

迄今為止,關(guān)于是否需要使用有源濾波器將低電壓 PLL 連接到高電壓 VCO 的話題引發(fā)了人們的激烈討論���。高電壓 PLL 日益得到廣泛應(yīng)用�,然而,這大大降低了有源濾波器的必要性��。其中一個(gè)示例就是 ADF4113HV PLL��,它集成了高電壓電荷泵��,并且具有 –212-dBc/Hz 的正常相位噪聲本底����。在此情況下��,PLL 電荷泵的輸出可以高達(dá) 15 V����,因此允許在 VCO 之前使用更簡(jiǎn)單的無源濾波器。

很快����,可將最大電壓增加到 30 V 的器件和具有高電壓電荷泵的小數(shù) N PLL 將會(huì)進(jìn)一步增強(qiáng)該高電壓 PLL 系列。如需了解更新內(nèi)容和新產(chǎn)品信息�,請(qǐng)參閱 PLL 網(wǎng)站。

具有集成 VCO 的寬帶 PLL

另一種將有源濾波器與高電壓 VCO 結(jié)合使用的備選方案是使用圖 2 中所示的完全集成式高性能 PLL����,例如 ADF4350�。在此情況下�����,VCO 集成到芯片上�����。通過使用多頻帶 VCO 方法���,避免了前面所討論的寬調(diào)諧范圍和低相位噪聲之間固有的利弊權(quán)衡問題�����。在 ADF4350 中�����,三個(gè)獨(dú)立的 VCO 集成在芯片上���,每個(gè) VCO 具有 16 個(gè)重疊的子帶,共有 48 個(gè)子帶�。每次更新頻率時(shí),均會(huì)啟動(dòng)自動(dòng)校準(zhǔn)以選擇合適的 VCO 子帶。

這顯示了將 VCO 設(shè)計(jì)從離散遷移到硅基解決方案的真正益處:可在最小的區(qū)域內(nèi)實(shí)現(xiàn)高度集成���,帶來了更高的設(shè)計(jì)靈活性�����。例如�����,ADF4350 還可以集成可編程的輸出分頻器級(jí),從而將頻率覆蓋范圍從 137.5 MHz 一直增加到 4.4 GHz — 對(duì)于希望在多個(gè)頻率和標(biāo)準(zhǔn)上重復(fù)使用同一設(shè)計(jì)的無線電設(shè)計(jì)師而言�����,這是一個(gè)非常具有吸引力的功能��。

與標(biāo)準(zhǔn) 12.7 mm 方形 VCO 封裝相比�,ADF4350 采用 5 mm 方形 LFCSP 封裝。性能水平已接近那些離散設(shè)計(jì)的水平�,100 kHz 偏置時(shí)的相位噪聲為 –114 dBc/Hz,1 MHz 偏置時(shí)的相位噪聲為 –134 dBc/Hz����。

圖 6. 顯示了 ADF4350 VCO 電壓中的 48 個(gè)不同子帶以及頻率關(guān)系。

如需詳細(xì)了解業(yè)界最廣泛的其中一種 PLL 產(chǎn)品組合,包括整數(shù) N���、小數(shù) N�、集成 VCO 和高電壓 PLL IC — 推動(dòng)性能更上一層樓并減輕全球 PLL 和無線電設(shè)計(jì)師面臨的設(shè)計(jì)挑戰(zhàn) — 請(qǐng)參閱 PLL 頻率合成器/VCO 網(wǎng)站���。

參考電路

1. 實(shí)用的無線電實(shí)驗(yàn)室論壇�����。 http://www.radio-labs.com���。

2. Best,Roland E�。 鎖相環(huán)。設(shè)計(jì)����、模擬和應(yīng)用。McGraw Hill�����。

3. Curtin��、Mike 和 Paul O’Brien。1999.“用于高頻接收器和發(fā)送器的鎖相環(huán)—第 2 部分�。”《模擬對(duì)話》,第 33 卷�。

4. 如需了解所有 ADI 器件的信息,請(qǐng)參閱 www.analog.com�。

推薦閱讀: