【導(dǎo)讀】本文簡(jiǎn)述功率在轉(zhuǎn)換器電路中的轉(zhuǎn)換傳輸過(guò)程,針對(duì)開關(guān)器件MOSFET在導(dǎo)通和關(guān)斷瞬間�,產(chǎn)生電壓和電流尖峰的問(wèn)題,進(jìn)而產(chǎn)生電磁干擾現(xiàn)象��,通過(guò)對(duì)比傳統(tǒng)平面MOSFET與超結(jié)MOSFET的結(jié)構(gòu)和參數(shù)���,尋找使用超結(jié)MOSFET產(chǎn)生更差。

本文簡(jiǎn)述功率在轉(zhuǎn)換器電路中的轉(zhuǎn)換傳輸過(guò)程���,針對(duì)開關(guān)器件MOSFET在導(dǎo)通和關(guān)斷瞬間���,產(chǎn)生電壓和電流尖峰的問(wèn)題,進(jìn)而產(chǎn)生電磁干擾現(xiàn)象��,通過(guò)對(duì)比傳統(tǒng)平面MOSFET與超結(jié)MOSFET的結(jié)構(gòu)和參數(shù)�,尋找使用超結(jié)MOSFET產(chǎn)生更差電磁干擾的原因,進(jìn)行分析和改善���。

隨著開關(guān)電源技術(shù)的不斷發(fā)展�����,功率MOSFET作為開關(guān)電源的核心電子器件之一����,開關(guān)損耗是其主要的損耗之一,本著節(jié)省能源��、降低損耗的基本思想���,功率MOSFET技術(shù)朝著提高開關(guān)速度��、降低導(dǎo)通電阻的方向發(fā)展�。COOL MOSFET是一種超結(jié)的新結(jié)構(gòu)功率MOSFET�����,具有更低的導(dǎo)通電阻�����,更快的開關(guān)速度���,可以實(shí)現(xiàn)更高的功率轉(zhuǎn)換效率���。然而�����,超結(jié)MOSFET超快的開關(guān)性能也帶來(lái)了不必要的副作用�,比如電壓�、電流尖峰較高,電磁干擾較差等����。

以下內(nèi)容以一個(gè)反激式轉(zhuǎn)換器拓?fù)洌ㄈ鐖D1)為例,簡(jiǎn)述轉(zhuǎn)換器的功率轉(zhuǎn)換傳輸過(guò)程��,從平面MOSFET與超結(jié)MOSFET的結(jié)構(gòu)和參數(shù)差別�����,討論電壓��、電流尖峰�,以及電磁干擾的產(chǎn)生機(jī)理��,通過(guò)外圍電路改善并降低電壓��、電流尖峰,從而實(shí)現(xiàn)降低電磁干擾的目的���。

圖1包含寄生元件的反激式轉(zhuǎn)換器拓?fù)鋱D

反激式轉(zhuǎn)換器工作原理

圖1為一個(gè)最簡(jiǎn)單的反激式轉(zhuǎn)換器拓?fù)浣Y(jié)構(gòu)��,并且包含以下寄生元件:如初級(jí)漏電感�、MOSFET的寄生電容和次級(jí)二極管的結(jié)電容��。該拓?fù)湓醋砸粋€(gè)升降壓轉(zhuǎn)換器����,將濾波電感替換為耦合電感,如帶有氣隙的磁芯變壓器����,當(dāng)主開關(guān)器件MOSFET導(dǎo)通時(shí),能量以磁通形式存儲(chǔ)在變壓器中��,并在MOSFET關(guān)斷時(shí)傳輸至輸出����。由于變壓器需要在MOSFET導(dǎo)通期間存儲(chǔ)能量,磁芯應(yīng)該開有氣隙,基于這種特殊的功率轉(zhuǎn)換過(guò)程��,所以反激式轉(zhuǎn)換器可以轉(zhuǎn)換傳輸?shù)墓β视邢?��,只是適合中低功率應(yīng)用�,如電池充電器、適配器和DVD播放器�����。

反激式轉(zhuǎn)換器在正常工作情況下����,當(dāng)MOSFET關(guān)斷時(shí),初級(jí)電流(id)在短時(shí)間內(nèi)為 MOSFET的Coss(即Cgd+Cds)充電,當(dāng)Coss兩端的電壓Vds超過(guò)輸入電壓及反射的輸出電壓之和(Vin+nVo)時(shí)����,次級(jí)二極管導(dǎo)通,初級(jí)電感Lp兩端的電壓被箝位至nVo����。因此初級(jí)總漏感Lk(即Lkp+n2×Lks)和Coss之間發(fā)生諧振�����,產(chǎn)生高頻和高壓浪涌����,MOSFET上過(guò)高的電壓可能導(dǎo)致故障��。

反激式轉(zhuǎn)換器可以工作在連續(xù)導(dǎo)通模式(CCM)(如圖2)和不連續(xù)導(dǎo)通模式(DCM)(如圖3)下���,當(dāng)工作在CCM模式時(shí),次級(jí)二極管保持導(dǎo)通直至MOSFET柵極導(dǎo)通�,而MOSFET導(dǎo)通時(shí),次級(jí)二極管的反向恢復(fù)電流被添加至初級(jí)電流��,因此在導(dǎo)通瞬間初級(jí)電流上出現(xiàn)較大的電流浪涌��;當(dāng)工作在DCM模式時(shí)�����,由于次級(jí)電流在一個(gè)開關(guān)周期結(jié)束前干涸���,Lp和MOSFET的Coss之間發(fā)生諧振���。

圖2 連續(xù)導(dǎo)通模式

圖3 不連續(xù)導(dǎo)通模式

圖4顯示了開關(guān)電源工作在DCM模式,實(shí)測(cè)的MOSFET電壓和電流工作波形���,除了可以看到MOSFET在開通和關(guān)斷的過(guò)程中�,均產(chǎn)生比較大的電壓和電流變化��,而且可以看到MOSFET在開通和關(guān)斷的瞬間,產(chǎn)生一些震蕩和電流尖峰�。

如圖1所示的包含寄生元件的反激式轉(zhuǎn)換器拓?fù)鋱D,其中Cgs�����、Cgd和 Cds分別為開關(guān)管MOSFET的柵源極��、柵漏極和漏源極的雜散電容����,Lp、Lkp�����、Lks和Cp分別為變壓器的初級(jí)電感��、初級(jí)電感的漏感��、次級(jí)電感的漏感和原邊線圈的雜散電容�,Cj為輸出二極管的結(jié)電容�。圖5為反激變換器工作在DCM工作模式時(shí),開關(guān)管分別工作在(a)開通瞬間�、 (b)開通階段����、 (c)關(guān)斷瞬間和(d)關(guān)斷階段時(shí)����,所對(duì)應(yīng)的等效分析電路,Rds為開關(guān)管的漏源極等效電阻���。

圖5 反激變換器在DCM模式開關(guān)管工作在各階段對(duì)應(yīng)的等效分析電路

在開關(guān)管開通瞬間�,由于電容兩端電壓不能突變��,雜散電容Cp兩端電壓開始是上負(fù)下正�,產(chǎn)生放電電流,隨著開關(guān)管逐漸開通��,電源電壓Vin對(duì)雜散電容Cp充電����,其兩端電壓為上正下負(fù),形成流經(jīng)開關(guān)管和Vin的電流尖峰���;同時(shí)Cds電容對(duì)開關(guān)管放電����,也形成電流尖峰,但是此尖峰電流不流經(jīng)Vin,只在開關(guān)管內(nèi)部形成回路�����;另外���,如果變換器工作在CCM模式時(shí)���,由于初級(jí)電感Lp兩端電壓縮小,二極管D開始承受反偏電壓關(guān)斷�,引起反向恢復(fù)電流,該電流經(jīng)變壓器耦合到原邊側(cè)����,也會(huì)形成流經(jīng)開關(guān)管和Vin的電流尖峰。

在開關(guān)管開通階段����,二極管D截止,電容Cp兩端電壓為Vin�����,通過(guò)初級(jí)電感Lp的電流指數(shù)上升,近似線性上升�����。

在開關(guān)管關(guān)斷瞬間����,初級(jí)電流id為Coss充電,當(dāng)Coss兩端的電壓超過(guò)Vin與nVo(二極管D開通時(shí)變壓器副邊線圈電壓反射回原邊線圈的電壓)之和時(shí)�����,二極管D在初級(jí)電感Lp續(xù)流產(chǎn)生的電壓作用下正偏開通����,Lk和Coss發(fā)生諧振,產(chǎn)生高頻震蕩電壓和電流�����。

在開關(guān)管關(guān)斷階段�����,二極管D正偏開通���,把之前存儲(chǔ)在Lp中的能量釋放到負(fù)載端����,此時(shí)副邊線圈電壓被箝位等于輸出電壓Vo,經(jīng)匝比為n的變壓器耦合回原邊���,使電容Cp電壓被充電至nVo(極性下正上負(fù))�����,初級(jí)電感Lp兩端的電壓被箝位至nVo��。當(dāng)Lp續(xù)流放電結(jié)束后���,D反偏截止,Lp和Coss�����、Cp發(fā)生諧振�����,導(dǎo)致Cp上的電壓降低�����。

功率MOSFET 的等效分析原理圖

MOSFET是電壓控制型器件,功率MOSFET的源�、漏電極不在同一平面內(nèi),也稱為縱向MOSFET(即VMOSFET),其具有很多不同于橫向MOSFET的特點(diǎn)���,一般把功率MOSFET看作一個(gè)由橫向MOSFET驅(qū)動(dòng)的縱向JFET器件,圖6顯示了功率MOSFET包含寄生器件在內(nèi)的等效原理圖��,其中Lg��、Ld�、Ls分別為MOSFET的柵極、漏極�、源極的引線電感,Rg為MOSFET內(nèi)部柵極電阻, Cgd���、Cgs��、Cds為MOSFET寄生電容�,D為寄生體二極管��。由于寄生器件的存在���,使功率MOSFET在反激變換器電路的工作和分析變得復(fù)雜�,特別是在變換瞬間,寄生參數(shù)的分析顯得更為重要�。

圖6 MOSFET包含寄生器件在內(nèi)的等效原理圖

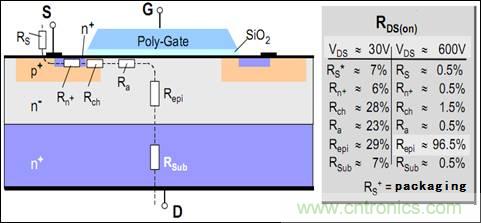

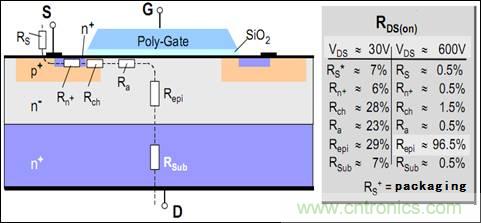

超結(jié) MOSFET 與平面MOSFET的區(qū)別 圖7顯示了平面MOSFET的截面結(jié)構(gòu)和電場(chǎng)分布,從中可以看出平面MOSFET的擊穿電壓取決于漂移區(qū)的摻雜度和厚度��,電場(chǎng)分布的傾斜度與漂移區(qū)摻雜度成正比�。因此,如需獲得較高的擊穿電壓�����,就需要較厚且輕摻雜的外延層��,但是從MOSFET的導(dǎo)通電阻分布(如圖8)中���,可以看出外延層的電阻占主要部分��,尤其是高擊穿電壓MOSFET����。

圖7 平面MOSFET的截面結(jié)構(gòu)和電場(chǎng)分布

圖8 MOSFET導(dǎo)通電阻分布

綜上所述����,平面高壓MOSFET由于結(jié)構(gòu)的原因����,導(dǎo)通電阻較大���,導(dǎo)致導(dǎo)通損耗較大����,而且開關(guān)速度也受到一定的限制�,開關(guān)損耗也比較大�,這顯然已經(jīng)不能滿足目前日益要求節(jié)能和提高轉(zhuǎn)換器效率的電子市場(chǎng)需求?����;谄矫鍹OSFET的缺點(diǎn)�,超結(jié)MOSFET應(yīng)運(yùn)而生,圖9給出了超結(jié)MOSFET的截面結(jié)構(gòu)和電場(chǎng)分布�����,與平面MOSFET的截面結(jié)構(gòu)不同�,超結(jié)MOSFET采用了較深的P型柱結(jié)構(gòu),平面MOSFET的外延層幾乎被交替的N型和P型半導(dǎo)體薄層替換�,平面MOSFET與超結(jié)MOSFET的等效器件模型如圖10所示����。

圖9 超結(jié)MOSFET的截面結(jié)構(gòu)和電場(chǎng)分布

圖10 MOSFET等效器件模型

超結(jié)MOSFET垂直方向上插入P型區(qū)��,可以補(bǔ)償過(guò)量的電流導(dǎo)通電荷���,在漂移層加反向偏置電壓�,將產(chǎn)生一個(gè)橫向電場(chǎng)�,使PN結(jié)耗盡,當(dāng)電壓達(dá)到一定值時(shí)�,漂移層完全耗盡,將起到電壓支持層的作用��,使器件的擊穿電壓僅依賴N-漂移區(qū)的厚度�����,而與N-區(qū)和P阱區(qū)的摻雜濃度無(wú)關(guān)�����,且這種電荷補(bǔ)償越充分�����,擊穿電壓越高。由于摻雜濃度的大幅提高�,在相同的擊穿電壓下,導(dǎo)通電阻Ron可以大大降低����,甚至突破硅限;同樣����,在相同的擊穿電壓和相同的導(dǎo)通電阻Ron下,可以使用更小的芯片面積���,從而減小柵電荷,提高開關(guān)速度���,降低驅(qū)動(dòng)功率和開關(guān)損耗�,表1顯示了西安芯派同型號(hào)芯片的SW Planer 系列和SW Cool系列MOSFET的參數(shù)對(duì)比結(jié)果�。

表1 SW Planer 系列MOSFET和SW Cool系列MOSFET的參數(shù)對(duì)比

反激式轉(zhuǎn)換器產(chǎn)生電磁干擾的原因和傳播方式

電磁干擾主要是傳導(dǎo)干擾和輻射干擾,傳導(dǎo)干擾是在輸入和輸出線上流過(guò)的干擾噪聲,來(lái)源于差模電流噪聲和共模電流噪聲�����;輻射干擾是通過(guò)空間輻射的干擾噪聲����,來(lái)源于電場(chǎng)發(fā)射和磁場(chǎng)發(fā)射,它們之間可以相互轉(zhuǎn)換��。

開關(guān)電源產(chǎn)生電磁干擾的原因較多�,其中以功率開關(guān)器件和變壓器為主要噪聲源。開關(guān)器件高頻的開通和關(guān)斷�����,導(dǎo)致電流和電壓的快速變化�����,電感及寄生電感的快速電流變化產(chǎn)生磁場(chǎng),從而產(chǎn)生較高的電壓尖峰uL=L×diL/dt�����;電容及寄生電容的快速電壓變化產(chǎn)生電場(chǎng)��,從而產(chǎn)生較高的電流尖峰iC=C×duC/dt���,而其內(nèi)部引線的雜散電感和寄生電容則是噪聲耦合的通道���,但是由于這些參數(shù)是器件固有的特性����,所以電子設(shè)計(jì)和應(yīng)用工程師無(wú)法對(duì)它們進(jìn)行優(yōu)化,只能根據(jù)器件手冊(cè)選擇匹配的器件���。前面已經(jīng)分析了開關(guān)管MOSFET 包含寄生器件的等效分析原理圖,超結(jié) MOSFET 與平面MOSFET的結(jié)構(gòu)和參數(shù)區(qū)別�,電磁干擾產(chǎn)生的原因,設(shè)計(jì)者可以根據(jù)情況選擇使用和優(yōu)化��。

變壓器作為另外一個(gè)主要噪聲源�,而初級(jí)次級(jí)的漏感����、初級(jí)的層間電容�����、次級(jí)的層間電容�����、初級(jí)和次級(jí)之間的耦合電容則是噪聲的通道��。如圖11所示的包含寄生電容的變壓器模型�����,其中Ca為最外層繞組到磁芯的電容����,Ct為輔助繞組到次級(jí)繞組的電容,Cs為初級(jí)繞組到次級(jí)繞組的電容��,Cp為初級(jí)繞組的層間電容�,Cm為最內(nèi)層初級(jí)繞組到磁芯的電容;除此之外,變壓器還有磁芯到大地的電容Cme����,輸出線到大地的電容Coe,初級(jí)或次級(jí)的層間電容可以通過(guò)減小繞組的層數(shù)來(lái)降低���,增大變壓器骨架窗口的寬度可以減小繞組的層數(shù)�。繞組的分離繞制���,如初級(jí)繞組采用三明治繞法���,可以減小初級(jí)的漏感,但由于增大了初級(jí)繞組和次級(jí)繞組的接觸面積����,因而增大了初級(jí)繞組和次級(jí)繞組的耦合電容。采用銅皮屏蔽(需連接到初級(jí)或次級(jí)的靜點(diǎn))可以減小初級(jí)繞組與次級(jí)繞組間的耦合電容����,但由于屏蔽層繞在初級(jí)繞組與次級(jí)繞組之間,使初級(jí)繞組和次級(jí)繞組的耦合系數(shù)降低���,從而又增加了漏感。

圖11 包含寄生電容的變壓器模型

差模電流在兩根輸入電源線(L、N)間反方向流動(dòng)��,構(gòu)成電流回路�����,其中一根是差模電流的源線����,則另一根是差模電流的回線,主要由開關(guān)器件的高頻開關(guān)電流產(chǎn)生�,圖12給出了開關(guān)管開通瞬間的差模電流流動(dòng)情況,可以看出IDM=ICp+ nIR−ICin ����;圖13給出了開關(guān)管關(guān)斷瞬間的差模電流流動(dòng)情況,可以看出IDM= ICds + Ig− ICp −ICin�。

圖12 開關(guān)管開通瞬間的差模電流

圖13 開關(guān)管關(guān)斷瞬間的差模電流

共模電流在輸入線、輸出線與大地間流動(dòng)�,主要由功率器件高頻工作的電壓瞬態(tài)變化產(chǎn)生,圖14給出了共模電流的流動(dòng)通道情況����,主要包括通過(guò)Cde、 Cm和Cme���、 Ca和Cme ���、 Ct和Coe��、 Cs和Coe產(chǎn)生共模電流�,其中通過(guò)Cs和Coe的共模電流占主導(dǎo)作用���。

圖14 共模電流產(chǎn)生通道

電場(chǎng)發(fā)射由du/dt產(chǎn)生�����,空間電容是電場(chǎng)發(fā)射的通道�����,其中共模電流可以產(chǎn)生相當(dāng)大的電場(chǎng)發(fā)射���。圖15給出了反激轉(zhuǎn)換器的主要電場(chǎng)發(fā)射源位置,其中初級(jí)繞組的電壓變化幅值大�,對(duì)于電場(chǎng)發(fā)射起主導(dǎo)作用。另外���,像手機(jī)充電器這類帶長(zhǎng)輸出線(1.8m)的產(chǎn)品�,長(zhǎng)的輸出導(dǎo)線也如同一個(gè)天線,可以將共模電流放大�,從而形成較大的共模電場(chǎng)發(fā)射�。

圖15 反激轉(zhuǎn)換器的主要電場(chǎng)發(fā)射源位置

磁場(chǎng)發(fā)射由高di/dt 的環(huán)路通過(guò)環(huán)路寄生電感產(chǎn)生,圖16給出了反激轉(zhuǎn)換器的主要磁場(chǎng)發(fā)射環(huán)路���,磁場(chǎng)發(fā)射方向符合右手定則�,其中次級(jí)側(cè)的電流變化幅值大���,對(duì)于磁場(chǎng)發(fā)射起主導(dǎo)作用��。另外���,變壓器的雜散磁場(chǎng)也是一個(gè)磁場(chǎng)發(fā)射源,主要由變壓器的氣隙產(chǎn)生���,例如E型磁芯在兩側(cè)開氣隙時(shí)雜散磁場(chǎng)大��,在中心柱開氣隙時(shí)雜散的磁場(chǎng)小�����。需特別注意����,高di/dt環(huán)路的寄生電感隨環(huán)路面積增大而增大,因此PCB的設(shè)計(jì)對(duì)于磁場(chǎng)發(fā)射非常關(guān)鍵����,次級(jí)側(cè)的電流環(huán)面積要盡量小,布線要盡量短粗���。

圖16 反激轉(zhuǎn)換器的主要磁場(chǎng)發(fā)射環(huán)路

改善使用超結(jié) MOSFET 的反激變換器的電磁干擾措施

通過(guò)對(duì)反激變換器的工作原理����,電磁干擾的產(chǎn)生原因�,MOSFET的等效原理圖,以及平面MOSFET與超結(jié)MOSFET的結(jié)構(gòu)和參數(shù)對(duì)比分析���,可以看出使用超結(jié)MOSFET雖然降低了反激變換器的損耗和驅(qū)動(dòng)功率��,但是由于開關(guān)管的開關(guān)速度提高����,增大了電壓和電流變化率���,使反激變換器的電磁干擾增強(qiáng)���。

電磁干擾的危害日益明顯和嚴(yán)重���,目前許多國(guó)家已經(jīng)把電磁干擾測(cè)量作為電子設(shè)備的強(qiáng)制測(cè)試項(xiàng)目,針對(duì)不同類型產(chǎn)品有不同的干擾限值要求��。電源作為電網(wǎng)與用電設(shè)備之間的接口電路���,在完成功率傳送和滿足電能變換的同時(shí),不可避免地產(chǎn)生電磁干擾�,但是改善和通過(guò)標(biāo)準(zhǔn)限值要求,也顯得尤為重要���。從反激變換器產(chǎn)生電磁干擾的原理出發(fā)���,降低電磁干擾的方法主要為降低電壓和電流的變化率;減小電路中存在的寄生電感和電容����;優(yōu)化PCB設(shè)計(jì)。

一���、減小電壓和電流變化率

減小電壓和電流變化率�����,可以通過(guò)改變柵極驅(qū)動(dòng)電阻�、改變變壓器結(jié)構(gòu)或者增加緩沖吸收電路實(shí)現(xiàn)。

(1)改變柵極電阻值可以改變開關(guān)管的開關(guān)速率�����,改變電壓和電流的變化率����,如圖17所示,在開關(guān)管的柵極外加驅(qū)動(dòng)電阻Rg=Rg1+Rg2,增加Rg,降低開關(guān)管的開通速度�,加快開關(guān)管的關(guān)斷速度。為了開關(guān)管的開通和關(guān)斷速度都降低���,可以如圖17所示����,給Rg2并聯(lián)一個(gè)低壓降快速恢復(fù)二級(jí)管����,如接成D1(實(shí)線)的方向,開關(guān)管開通時(shí)柵極驅(qū)動(dòng)電阻為Rg,關(guān)斷時(shí)柵極驅(qū)動(dòng)電阻為Rg1�,開關(guān)管關(guān)斷時(shí)的速度相對(duì)不并二極管時(shí)要慢。

圖17 改變柵極驅(qū)動(dòng)電阻

(2)在反激變換器的開關(guān)管關(guān)斷瞬間����,由于變壓器的初級(jí)漏感Lk和開關(guān)管的寄生輸出電容Coss構(gòu)成了一個(gè)串聯(lián)諧振電路,會(huì)產(chǎn)生非常高的過(guò)壓和振鈴���,電路的Q值越高���,振鈴電壓就越高�。這種過(guò)高的振鈴電壓可能會(huì)造成巨大的電磁干擾,并且由于MOSFET漏電壓的升高���,甚至?xí)档烷_關(guān)管的可靠性����。

改變變壓器的結(jié)構(gòu)����,給變壓器的初級(jí)繞組增加一個(gè)恢復(fù)繞組NR=Np,使兩個(gè)繞組成為雙股����,并排纏繞在磁芯或線軸上��,形成雙股繞組�����。如圖18所示��,NR一端與初級(jí)地相連����,與Np同名的一端通過(guò)一個(gè)二極管D1連接到Vin��。這種方法使耦合最大化����,并獲得了寄生電容與電感的嚴(yán)格匹配,初級(jí)繞組與其它繞組之間的耦合并沒有那么重要�。

圖18 增加恢復(fù)繞組NR和二極管D1實(shí)現(xiàn)無(wú)源阻尼器

如圖19所示,圖(a)顯示了開關(guān)管關(guān)斷時(shí)���,初級(jí)電流(通道2����,紅色波形)為Coss充電后,在MOSFET的漏極(Vds�,通道1,藍(lán)色波形)有振鈴��。圖(b)中���,通道1仍為Vds����,Coss的充電使通過(guò)D的次級(jí)電流(通道2)延遲了約100ns����。圖(c)中,恢復(fù)繞組NR直接繞過(guò)寄生電容Coss����,將積累的泄漏能量導(dǎo)回電源軌�����,并箝位開關(guān)電壓(通道1)��,由于Np=NR��,所以將Vds限制在Vin的兩倍,而初級(jí)電流的負(fù)浪涌(通道2)事實(shí)上是從恢復(fù)繞組流出的電流���。圖(d)中��,次級(jí)二極管D馬上變?yōu)檎?���,泄漏磁通阻止了電流的傳輸�,次?jí)電流(通道2)達(dá)到一個(gè)均衡的峰值,直到漏泄能量被完全恢復(fù)����,初級(jí)電流降為零。

圖19 增加恢復(fù)繞組NR與無(wú)恢復(fù)繞組的開關(guān)電壓與電流對(duì)比

(3)緩沖吸收電路改變高頻電壓和電流的變化率��,如圖20所示��,在變壓器的初級(jí)繞組并聯(lián)RCD箝位電路�����,可以抑止由于變壓器初級(jí)漏感在開關(guān)管關(guān)斷過(guò)程中產(chǎn)生的電壓尖峰����;L1��、L2 和L3可以降低高頻電流變化率����,但是L1和L2只對(duì)特定的頻帶起作用�,而L3只對(duì)工作于CCM模式才有效; R1C1���,R2C2����,R3C3����,R4C4 和 C5可以降低相應(yīng)的功率器件兩端的高頻電壓變化率。特別注意的是�����,所有的這些緩沖吸引電路都需要消耗一定功率��,產(chǎn)生附加的功率損耗��,降低系統(tǒng)的效率�;同時(shí)也增加元件數(shù)量、PCB尺寸和系統(tǒng)成本���,因此必須根據(jù)實(shí)際需要選擇使用�����。

圖20 增加緩沖吸收電路

二�、減小寄生的電感和電容值

從差模電流與共模電流的產(chǎn)生原因和流動(dòng)方向分析���,以下建議幾種減小差模電流和共模電流的方法�����,設(shè)計(jì)者可以根據(jù)需要和實(shí)際情況選擇使用�。

(1)差模濾波器可以濾除差模電流�����,如圖21所示�����,差模濾波器是由電感和電容組成的二階低通濾波器�����,由于其電感有雜散電容,對(duì)高頻干擾噪聲可以由雜散電容旁路��,使濾波器不能起到有效的作用���,采用幾個(gè)電解電容并聯(lián)可以減小ESL和 ESR��,降低開關(guān)電流的高次諧波因?yàn)檩斎腚娊怆娙莸腅SL和ESR形成的差模電流�����。

圖21 降低差模電流的新結(jié)構(gòu)變壓器

(2)改變變壓器結(jié)構(gòu)(如圖22)降低開關(guān)管開通和關(guān)斷瞬間的差模電流����。

圖22 降低差模電流的新結(jié)構(gòu)變壓器

(3)在L與N線之間并聯(lián)X電容���,可以濾除差模干擾��。

(4)MOSFET采用源極連接芯片基體用于散熱�����,而不采用漏極����,且PCB布線時(shí)減小漏極區(qū)銅皮面積����,目的是減小Cde,降低共模電流����。

(5)改變變壓器結(jié)構(gòu)降低共模電流,如圖23所示����,調(diào)整輔助繞組和次級(jí)繞組的整流二極管放置位置,從而改變電壓變化方向�,改變動(dòng)點(diǎn)位置,且注意靜點(diǎn)盡量靠近�,減小總體的共模電流;另外����,在內(nèi)層放置銅皮,銅皮的寬度小于或等于初級(jí)繞組的寬度���,銅皮的中點(diǎn)由導(dǎo)線連接到靜點(diǎn)����,同時(shí)可以在初級(jí)繞組和次級(jí)繞組、輔助繞組和次級(jí)繞組之間繞制屏蔽繞組(也可是銅皮�����,方法與內(nèi)層放置銅皮一致)�����,繞滿一層即可�����,一端連接到靜點(diǎn)�,一端懸空內(nèi)埋,減小總體的共模電流����,但是屏蔽層的使用必須滿足效率的要求,因?yàn)槠帘螌拥氖褂脮?huì)降低初次級(jí)的耦合系數(shù)��,降低轉(zhuǎn)換效率����。

圖23 降低共模電流的新結(jié)構(gòu)變壓器

(6)在初次級(jí)之間加入 Y電容��,如圖24所示, 通過(guò)Cs的大部分共模電流被Y 電容旁路���,返回到初級(jí)的地�����,因?yàn)閅電容的值遠(yuǎn)大于Coe��。Y電容必須直接或盡量用短的直線連接到初級(jí)和次級(jí)的靜點(diǎn)��,一般是開關(guān)管開通時(shí)的dV/dt大于關(guān)斷時(shí)的dV/dt �,Y電容連接到初級(jí)的地,反之連接到Vin�����。

圖24 Y電容對(duì)流過(guò)初次級(jí)共模電流的作用

三����、優(yōu)化PCB設(shè)計(jì)

PCB設(shè)計(jì)對(duì)于電磁干擾的產(chǎn)生非常關(guān)鍵,以下建議幾種降低電磁干擾的PCB設(shè)計(jì)方法�,設(shè)計(jì)者可以根據(jù)需要和實(shí)際情況選擇使用。

(1)輸入端與輸出端的邊線應(yīng)避免相鄰平行,以免產(chǎn)生反射干擾���,必要時(shí)應(yīng)加地線隔離�����。

(2)按照電路的流程安排各個(gè)功能電路單元的位置����,圖25給出了反激轉(zhuǎn)換器內(nèi)部的四個(gè)電流環(huán)路�����,分別是功率開關(guān)管交流電流環(huán)路�、輸出整流器交流電流環(huán)路、輸入電源電流環(huán)路和輸出負(fù)載電流環(huán)路�����,每個(gè)環(huán)路要與其他環(huán)路分開�,其中輸入環(huán)路與功率開關(guān)環(huán)路必須直接接到輸入電容的兩端;輸出環(huán)路與整流環(huán)路的連接必須直接接到輸出電容的兩端���;開關(guān)環(huán)路的濾波電容�、功率開關(guān)管和變壓器必須盡可能靠近放置;輸出整流環(huán)路的整流器����、電感和濾波電容必須盡可能靠近放置,放置時(shí)需確定好器件方向�����,使其之間的電流通路盡可能短����。

圖25 反激轉(zhuǎn)換器內(nèi)部的主要電流環(huán)路

(3)兩相鄰層的布線要互相垂直���,平行容易產(chǎn)生寄生耦合�����。

(4)盡量減小高di/dt環(huán)路�����,并采用寬的布線有利于減小差模干擾�。

(5)避免直角走線��,直角走線會(huì)使傳輸線的線寬發(fā)生變化,造成阻抗不連續(xù)�����,對(duì)信號(hào)的影響主要體現(xiàn)在:拐角可以等效為傳輸線上的容性負(fù)載�����,減緩上升時(shí)間�����;阻抗不連續(xù)會(huì)造成信號(hào)的反射����;直角尖端產(chǎn)生的EMI。

(6)開關(guān)電源內(nèi)部接地的合理性直接影響到電源的電磁干擾甚至影響其穩(wěn)定工作����,圖26給出了反激轉(zhuǎn)換器的地線安排情況,其中電源地是電流環(huán)路底下的支路��;控制地是連接控制集成電路和與之相關(guān)的無(wú)源器件的地����?��?刂频胤浅C舾校蚨谄渌慕涣麟娏鳝h(huán)路都布置好后再放置�,必須通過(guò)一些特定的點(diǎn)與其他地連接,這個(gè)連接點(diǎn)是產(chǎn)生控制IC所要檢測(cè)的小電壓的所有器件的公共連接點(diǎn)�,包括電流型變換器電流檢測(cè)電阻的公共接點(diǎn)和輸出端電阻分壓器的下端。除此之外��,每條大電流的地線要短而寬����,輸入濾波電容的公共端應(yīng)作為其他交流電流地的唯一接點(diǎn)。

圖26 反激轉(zhuǎn)換器的地線安排

(7)在電源的PCB底層鋪銅皮或額外加一塊銅皮或單面板��,可以有效的減小電場(chǎng)發(fā)射和共模電流(如圖27)����。

圖27 減小電場(chǎng)發(fā)射

推薦閱讀: