【導(dǎo)讀】當(dāng)運(yùn)算放大器的輸入電壓超過(guò)額定輸入電壓范圍,或者在極端情況下��,超過(guò)放大器的電源電壓時(shí),放大器可能發(fā)生故障甚至受損��。本文討論過(guò)壓狀況的一些常見(jiàn)原因和影響���,為無(wú)保護(hù)的放大器增加過(guò)壓保護(hù)是如何的麻煩����,以及集成過(guò)壓保護(hù)的新型放大器如何能為設(shè)計(jì)工程師提供緊湊�、魯棒、透明�、高性價(jià)比的解決方案。

所有電子器件的可耐受電壓都有一個(gè)上限�,超過(guò)上限就會(huì)產(chǎn)生影響,輕則導(dǎo)致工作暫時(shí)中斷或系統(tǒng)閂鎖�����,重則造成永久性損害���。特定器件能夠耐受的過(guò)壓量取決于多個(gè)因素�,包括是否安裝或意外接觸器件��、過(guò)壓事件的幅度和持續(xù)時(shí)間����、器件的魯棒性等����。

精密放大器常常是傳感器測(cè)量信號(hào)鏈中的第一個(gè)器件���,因而最容易受到過(guò)壓故障的影響����。選擇精密放大器時(shí)����,系統(tǒng)設(shè)計(jì)師必須了解放大器的共模輸入范圍。在數(shù)據(jù)手冊(cè)中��,共模輸入范圍可能是用輸入電壓范圍(IVR), 測(cè)試條件下的共模抑制比(CMRR),或以上二者來(lái)規(guī)定����。.

過(guò)壓狀況的實(shí)際原因

放大器需要兩種保護(hù):一是過(guò)壓保護(hù) 用以防止電源時(shí)序控制、休眠模式切換和電壓尖峰引起的故障���;二是 ESD 靜電放電)保護(hù),用以防止靜電放電 (甚至搬運(yùn)過(guò)程中也可能出現(xiàn)靜電放電),引起的故障���。 安裝后, 器件可能會(huì)受系統(tǒng)電源時(shí)序控制�����,導(dǎo)致重復(fù)性過(guò)壓應(yīng)力����。系統(tǒng)設(shè)計(jì)師必須想方設(shè)法使故障電流避開(kāi)敏感的器件,或者限制故障電流����,使其不致于損壞器件。

在有多個(gè)電源電壓的復(fù)雜分布式電源架構(gòu) (DPA)系統(tǒng)中, 電源時(shí)序控制可以使系統(tǒng)電路各部分的電源在不同的時(shí)間開(kāi)啟和關(guān)閉����。時(shí)序控制不當(dāng)可能會(huì)導(dǎo)致某個(gè)器件的某個(gè)引腳發(fā)生過(guò)壓或閂鎖狀況。

隨著人們?cè)絹?lái)越關(guān)注能源效率�,許多系統(tǒng)要求實(shí)現(xiàn)復(fù)雜的休眠 和待機(jī) 模式。這意味著�,在系統(tǒng)的某些部分已關(guān)斷的同時(shí),其它部分仍然可能處于上電和活動(dòng)狀態(tài)��。與電源時(shí)序控制一樣���,這些情況可能會(huì)導(dǎo)致無(wú)法預(yù)測(cè)的過(guò)壓事件���,但主要是在輸入引腳上�。

許多類型的傳感器會(huì)產(chǎn)生意想不到的���、與它們要測(cè)量的物理現(xiàn)象無(wú)關(guān)的輸出尖峰�����,這類過(guò)壓狀況一般僅影響輸入引腳���。

靜電放電是一種廣為人知的過(guò)壓事件,常常發(fā)生在安裝器件之前�。它造成的損害非常廣泛,以至于業(yè)界主要規(guī)范�����,如JESD22-A114D等��,不得不明確如何測(cè)試和規(guī)定半導(dǎo)體耐受各類ESD事件的能力���。幾乎所有半導(dǎo)體產(chǎn)品都包含某種形式的集成保護(hù)器件�����。應(yīng)用筆記AN-397("標(biāo)準(zhǔn)線性集成電路的電誘發(fā)損壞:最常見(jiàn)起因和防止再發(fā)生的相關(guān)處理,"是一篇很好的參考文獻(xiàn)�����,詳細(xì)討論了這一問(wèn)題�。出現(xiàn)高能脈沖時(shí)����,ESD單元應(yīng)進(jìn)入低阻抗?fàn)顟B(tài)。這不會(huì)限制輸入電流�����,但能提供到供電軌的低阻抗路徑���。

一個(gè)簡(jiǎn)單的案例研究:電源時(shí)序控制

隨著混合信號(hào)電路變得無(wú)處不在����,單一PCB上的多電源需求也變得非常普遍�。關(guān)于新設(shè)計(jì)需要考慮的一些微妙問(wèn)題,特別是需要許多不相關(guān)的電源時(shí)��,請(qǐng)參閱應(yīng)用筆記AN-932 "電源時(shí)序控制,".

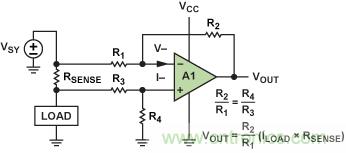

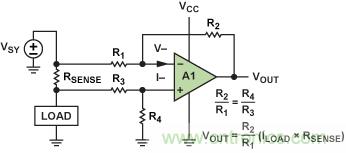

精密放大器可能會(huì)成為這種狀況的受害者�����。圖1顯示了一個(gè)配置成差分放大器的運(yùn)算放大器。放大器通過(guò)RSENSE檢測(cè)電流�,并提供與相應(yīng)壓降成比例的輸出。必須采取措施����,確保由R3和R4構(gòu)成的分壓器將輸入偏置在額定IVR范圍內(nèi)的某處。如果放大器的電源電壓不是從VSY, 獲得,并且VCC在VSY,之后出現(xiàn)����,則A1反相輸入端的電壓為:

V– = VSY – (I– × R1) (1)

其中I–由無(wú)電源時(shí)A1的輸入阻抗決定。如果放大器不包含過(guò)壓處理設(shè)計(jì)��,則最有可能的電流路徑是通過(guò)ESD二極管�、箝位二極管或寄生二極管流向電源或地。如果此電壓超出IVR范圍���,或者電流超過(guò)數(shù)據(jù)手冊(cè)規(guī)定的額定最大值����,器件可能會(huì)受損��。

ADA4091 和 ADA4096, 等過(guò)壓保護(hù)放大器所用的ESD結(jié)構(gòu)不是二極管,而是 DIAC等過(guò)壓保護(hù)放大器所用的ESD結(jié)構(gòu)不是二極管���,而是

圖1. 差分放大器高端電流傳感器�。如果VSY先于VCC,上電�,放大器的輸入電壓或電流可能會(huì)超過(guò)數(shù)據(jù)手冊(cè)規(guī)定的最大值

運(yùn)算放大器中的故障狀況

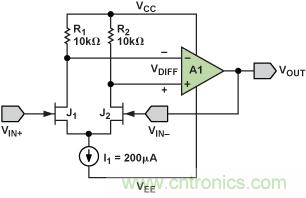

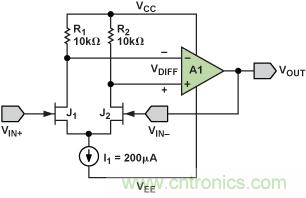

圖2顯示了一個(gè)N溝道JFET輸入級(jí) (J1, J2, R1, and R2), 后接一個(gè)第二增益級(jí)和輸出緩沖器(A1)����。當(dāng)開(kāi)環(huán)放大器在其額定IVR范圍內(nèi)時(shí),差分輸入信號(hào) (VIN+ – VIN–)與VDIFF.180度異相���。連接為單位增益緩沖器時(shí)(如圖所示)���,如果VIN+的共模電壓超過(guò)放大器的IVRJ1''的柵極-漏極進(jìn)入未夾斷狀態(tài)并傳導(dǎo)整個(gè)200 µA級(jí)電流。只要J1''的柵極-漏極電壓仍然反向偏置VIN+的進(jìn)一步增加就不會(huì)導(dǎo)致 VDIFF變化 (VOUT仍然處于正供電軌). 然而���,一旦J1''的柵極-漏極變?yōu)檎?��,VIN+的進(jìn)一步增加就會(huì)提高A1反相輸入端的電壓,導(dǎo)致輸入信號(hào)與 VDIFF之間發(fā)生不需要的反相.

圖2. N溝道JFET輸入運(yùn)算放大器結(jié)構(gòu)示意圖

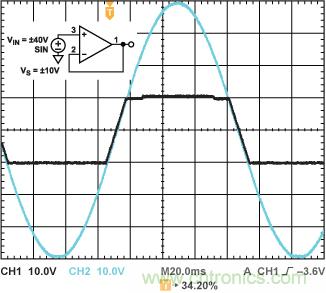

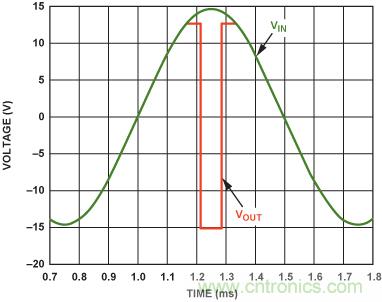

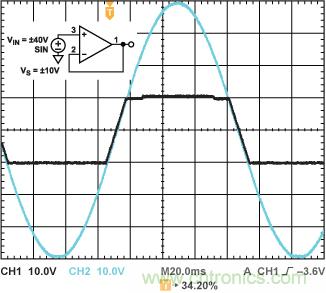

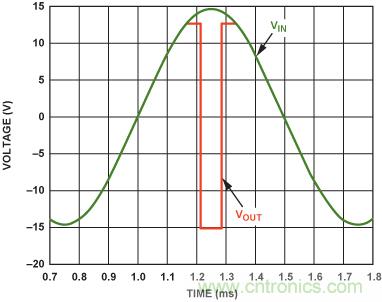

圖3顯示了A1輸出端反相的一個(gè)示例�。與雙極性輸入放大器不同,JFET放大器的輸入未箝位�,因而易發(fā)生反相。CMOS放大器的柵極與漏極電隔離,一般不會(huì)發(fā)生反相����。如果確實(shí)會(huì)發(fā)生反相,運(yùn)算放大器制造商一般會(huì)在數(shù)據(jù)手冊(cè)中說(shuō)明�。下列條件下可能發(fā)生反相:放大器輸入端不是CMOS,最大差分輸入為VSY, 數(shù)據(jù)手冊(cè)未聲明不會(huì)發(fā)生反相���。雖然反相本身不是破壞性的���,但它能導(dǎo)致正反饋,進(jìn)而使伺服環(huán)路不穩(wěn)定.

圖3. 當(dāng)VIN超過(guò)額定IVR時(shí)�����,輸入反相導(dǎo)致放大器輸出負(fù)值

系統(tǒng)設(shè)計(jì)師還必須關(guān)注放大器輸入超出電源范圍時(shí)會(huì)發(fā)生什么��。這種故障狀況通常發(fā)生在電源時(shí)序控制導(dǎo)致一個(gè)源信號(hào)先于放大器電源激活時(shí)�����,或者在開(kāi)啟�、關(guān)閉或工作中電源出現(xiàn)尖峰時(shí)。對(duì)于大多數(shù)放大器��,這種狀況是破壞性的,尤其是如果過(guò)壓大于二極管壓降����。

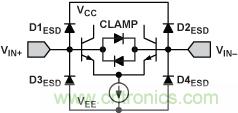

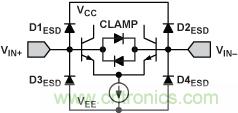

圖4顯示了一個(gè)帶ESD保護(hù)二極管和箝位二極管的典型雙極性輸入級(jí)。在緩沖器配置中�����,當(dāng)VIN+ 超過(guò)任一電源軌時(shí)��,ESD和箝位二極管就會(huì)正偏��。這些二極管的源極阻抗非常低�,源極支持多少電流�,二極管就能傳導(dǎo)多少電流。精密放大器AD8622提供少許差分保護(hù)����,輸入端串聯(lián)500 Ω電阻,施加差分電壓時(shí)��,該電阻可限制輸入電流���,但它只能在輸入電流不超過(guò)額定最大值時(shí)提供保護(hù)���。如果最大輸入電流為5 mA���,則允許的最大差分電壓為5 V。注意�,這些電阻并不與ESD二極管串聯(lián),因而無(wú)法限制流向電源軌的電流(例如在過(guò)壓期間)����。

圖4. 帶ESD和差分保護(hù)二極管的雙極性輸入級(jí)

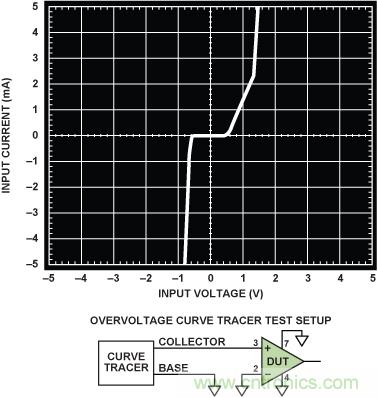

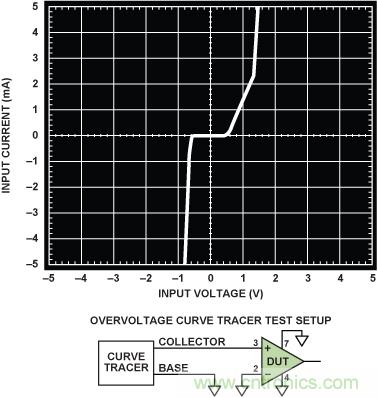

圖5顯示一個(gè)無(wú)保護(hù)雙極性運(yùn)算放大器在同時(shí)施加差分輸入和過(guò)壓情況下的輸入電流與電壓的關(guān)系。一旦施加的電壓超過(guò)二極管壓降����,電流就可能損害、降低運(yùn)算放大器的性能���,甚至破壞運(yùn)算放大器��。

圖5. 差分輸入電壓超過(guò)二極管壓降時(shí)的運(yùn)算放大器輸入電流

外部輸入過(guò)壓保護(hù)

從半導(dǎo)體運(yùn)算放大器問(wèn)世之初��,IC設(shè)計(jì)師就不得不權(quán)衡芯片架構(gòu)與應(yīng)對(duì)其脆弱性所需的外部電路之間的關(guān)系�。故障保護(hù)一直是最棘手的問(wèn)題例如�,, 請(qǐng)參閱 "運(yùn)算放大器輸出反相和輸入過(guò)壓保護(hù)"和MT-069, "儀表放大器輸入過(guò)壓保護(hù)").

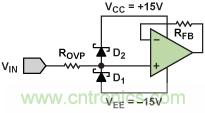

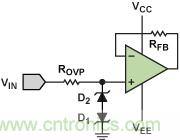

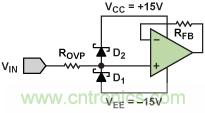

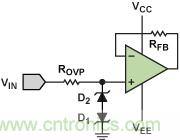

系統(tǒng)設(shè)計(jì)師之所以需要精密運(yùn)算放大器,是因?yàn)樗袃蓚€(gè)重要特性:低失調(diào)電壓(VOS)和高共模抑制比(CMRR)�,這兩個(gè)特性能夠簡(jiǎn)化校準(zhǔn)并使動(dòng)態(tài)誤差最小��。為在存在電氣過(guò)應(yīng)力(EOS)的情況下保持這些特性����,雙極性運(yùn)算放大器經(jīng)常內(nèi)置箝位二極管���,并將小限流電阻與其輸入端串聯(lián)���,但這些措施無(wú)法應(yīng)對(duì)輸入電壓超過(guò)供電軌時(shí)引起的故障狀況。為了增加保護(hù)�,系統(tǒng)設(shè)計(jì)師可以采用圖6所示的電路。

圖6. 利用限流電阻和兩個(gè)肖特基二極管提供外部保護(hù)的精密運(yùn)算放大器�����。RFB與ROVP相等����,從而平衡輸入偏置電流引起的失調(diào)

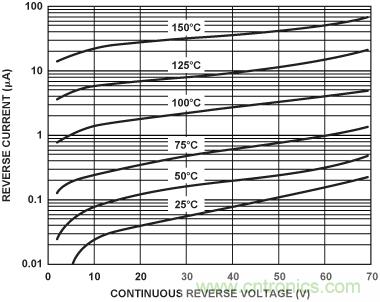

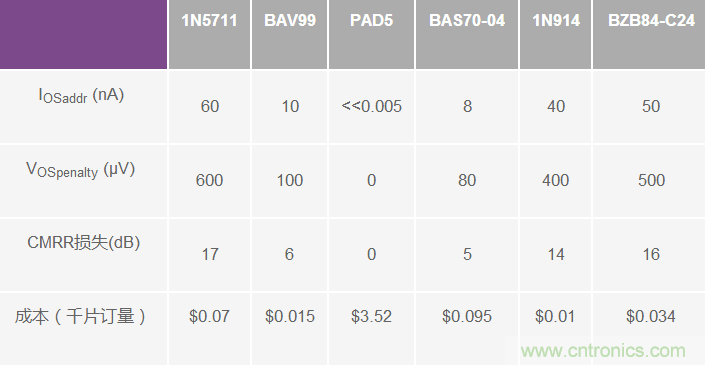

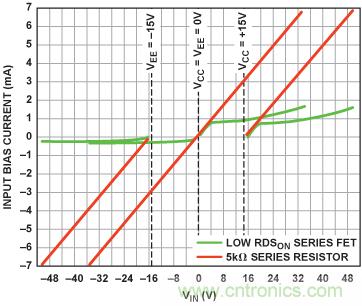

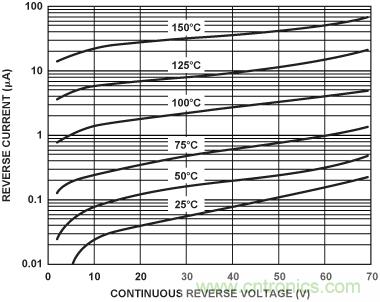

如果VIN處的信號(hào)源先行上電�,ROVP將限制流入運(yùn)算放大器的電流。肖特基二極管的正向電壓比典型的小信號(hào)二極管低200 mV���,因此所有過(guò)壓電流都會(huì)通過(guò)外部二極管D1和D2.分流�����。然而���,這些二極管可能會(huì)降低運(yùn)算放大器的性能��。例如�����,可以利用1N5711的反向漏電流曲線(見(jiàn)圖7)來(lái)確定特定過(guò)壓保護(hù)電阻造成的CMRR損失���。1N5711在0 V時(shí)的反向漏電流為0 nA,在30 V時(shí)為60 nA�。對(duì)于0 V共模電壓, D1 和 D2 引起的額外IOS取決于其漏電流的匹配程度��。當(dāng)V被拉至+15 V時(shí)��,D1將反向偏置30 V���,D2將偏置0 V�。因此����,額外的60 nA電流流入ROVP.當(dāng)輸入被拉至–15 V時(shí)�����,D1和D2 的電氣位置交換�,60 nA電流流出ROVP. 在任意共模電壓下���,保護(hù)二極管引起的額外 IOS等于:

IOSaddr = ID1 – ID2 (2)

圖7. 1N5711反向電流與連續(xù)反向電壓之間的關(guān)系

由公式2可計(jì)算出極端共模電壓下的VOS損失:

VOSpenalty = IOSaddr × ROVP (3)

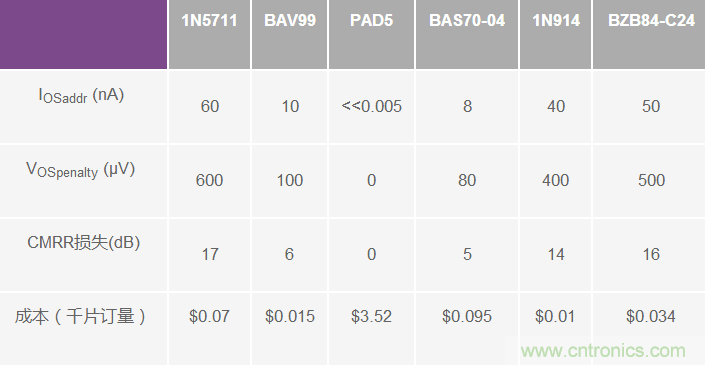

使用1N5711在30 V時(shí)的漏電流60 nA以及5 kΩ保護(hù)電阻����,兩個(gè)極端共模電壓下的VOS將增加300 µV���,導(dǎo)致整個(gè)輸入電壓范圍內(nèi)的額外 ?VOS 為600 μV����。根據(jù)數(shù)據(jù)手冊(cè)���,一個(gè)具有110 dB CMRR的運(yùn)算放大器將損失17 dB CMRR。插入反饋電阻來(lái)均衡源阻抗只能在共模電壓為0 V時(shí)有幫助����,但無(wú)法防止整個(gè)共模范圍內(nèi)產(chǎn)生額外的IOS表1顯示了保護(hù)精密放大器常用的一些二極管的計(jì)算結(jié)果�����。對(duì)于CMRR損失計(jì)算����,假設(shè)使用5 kΩ保護(hù)電阻���。

表1. 常用保護(hù)二極管及其對(duì)110 dB CMRR精密運(yùn)算放大器的影響

圖6所示的方法可能還有一個(gè)缺點(diǎn)����,那就是保護(hù)二極管會(huì)將過(guò)壓電流分流到電源中��。例如��,如果正電源無(wú)法吸收大量電流�,過(guò)壓電流就可能迫使正電源電壓提高。

防止這一現(xiàn)象的一種方法是在正輸入與地之間使用背靠背齊納二極管�����,如圖8所示���。超過(guò)D1或 D2的齊納電壓時(shí)�����,二極管將過(guò)壓電流分流到地��,從而保護(hù)電源�。這種配置能夠防止過(guò)壓期間的電荷泵效應(yīng),但齊納二極管的漏電流和電容高于小信號(hào)二極管�。此外,齊納二極管的漏電流曲線具有軟拐點(diǎn)(soft-knee)特征��。在放大器的共模范圍內(nèi)����,這會(huì)帶來(lái)額外的CMRR損失,如前所述�。例如,BZB84-C24是一個(gè)背靠背齊納二極管對(duì)���,工作電壓范圍為22.8 V至25.6 V��,反向電流額定值為50 nA(最大值���,16.8 V時(shí))�����,但制造商并未說(shuō)明接近齊納電壓時(shí)的漏電流是多少。此外�,為實(shí)現(xiàn)更陡的擊穿特性,齊納二極管一般采用比小信號(hào)二極管摻雜更重的擴(kuò)散工藝制造����,這就導(dǎo)致寄生電容相對(duì)較高,因而失真(特別是在幅度較高時(shí))和失穩(wěn)的可能性更高���。

圖8. 利用限流電阻和兩個(gè)齊納二極管提供外部保護(hù)的精密運(yùn)算放大器

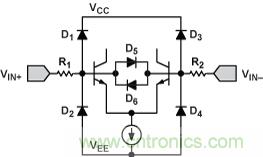

早期集成過(guò)壓保護(hù)

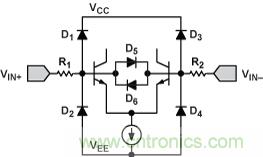

上面討論了放大器的一些常用外部保護(hù)方法的缺點(diǎn)�。如果放大器本身的設(shè)計(jì)能夠耐受較大的輸入過(guò)壓�,那么其中的一些缺點(diǎn)是可以避免的。圖9顯示了差分輸入對(duì)采用的常見(jiàn)集成保護(hù)方案����。

圖9. 帶阻性過(guò)壓保護(hù)的差分輸入對(duì)(未顯示ESD保護(hù))

在該電路中,兩個(gè)放大器輸入端均有輸入保護(hù)電阻�����。雖然一般情況下只有一個(gè)輸入端需要過(guò)壓保護(hù)�,但使各輸入端的寄生電容和漏電流均衡可以降低失真和失調(diào)電流。此外,二極管不必處理ESD事件��,因而可以相對(duì)較小�。

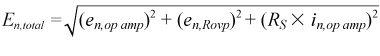

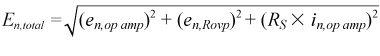

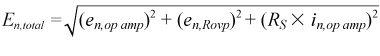

增加電阻,無(wú)論是外置還是內(nèi)置�,均會(huì)增加放大器的和方根(RSS)熱噪聲(公式4):

(4)

如果使用1 kΩ電阻來(lái)保護(hù)噪聲為4 nV/√Hz的運(yùn)算放大器,總電壓噪聲將提高√2倍�。集成保護(hù)電阻并不能改變過(guò)壓保護(hù)會(huì)提高等效輸入電壓噪聲的事實(shí),但將R1和R2 與運(yùn)算放大器集成在一起可確保數(shù)據(jù)手冊(cè)的噪聲規(guī)格包括保護(hù)電路�。

為了避免權(quán)衡噪聲與過(guò)壓,需要這樣一種保護(hù)電路:當(dāng)放大器輸入在額定范圍內(nèi)時(shí)�,它提供低電阻;當(dāng)放大器輸入超過(guò)供電軌時(shí)��,它提供高電阻��。這種特性將能按需改善過(guò)壓保護(hù)��,降低正常工作時(shí)的總噪聲貢獻(xiàn)���。圖10顯示了一種具有該特性的電路方案.

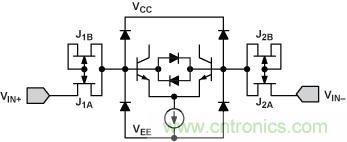

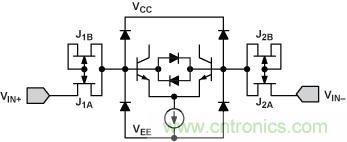

圖10. 帶主動(dòng)過(guò)壓保護(hù)的輸入差分對(duì)

Jxy全部是P溝道JFET�����,它們是耗盡型器件��,因此溝道的摻雜類型與源極和漏極相同�。當(dāng)放大器輸入電平介于兩個(gè)供電軌之間時(shí)�����,J1A和J2A是簡(jiǎn)單的電阻���,阻值等于RDSON 因?yàn)檩斎肫秒娏髯銐蛐?��,溝道與柵極之間的任何電位差都不會(huì)使溝道關(guān)閉。如果VIN+ 超出負(fù)電源一個(gè)二極管壓降�,電流就會(huì)流過(guò)J1A,導(dǎo)致漏極關(guān)閉。這種轉(zhuǎn)換實(shí)際上是 J1A離開(kāi)三極工作區(qū)���,進(jìn)入線性工作區(qū)�����。如果VIN+超出正電源一個(gè)二極管壓降��,J1A將充當(dāng)橫向PNP�。VIN+至柵極將用作正偏射極-基極結(jié)�,另一個(gè)結(jié)用作基極-集電極,其高阻值避免輸入管過(guò)壓。

圖11. FET保護(hù)運(yùn)算放大器在受到直流過(guò)壓掃描時(shí)的有效輸入阻抗

集成的優(yōu)勢(shì)

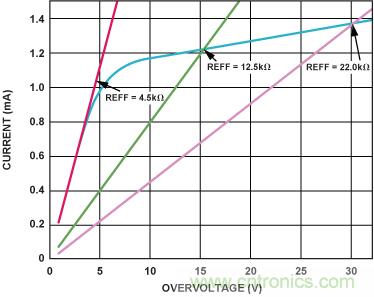

ADA4091和ADA4096等放大器證明���,實(shí)現(xiàn)魯棒的輸入過(guò)壓保護(hù)對(duì)運(yùn)算放大器的精度影響非常?。ㄈ鐖D10所示)���。ADA4096能夠提供與電源電平無(wú)關(guān)的32 V過(guò)壓保護(hù)���,從而無(wú)需雖然廉價(jià)但會(huì)大幅降低放大器精度的外部器件,或者雖然精密但成本高于放大器本身的外部器件����。

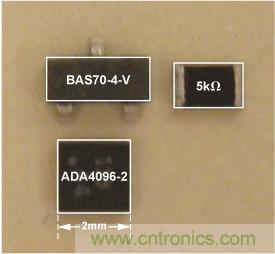

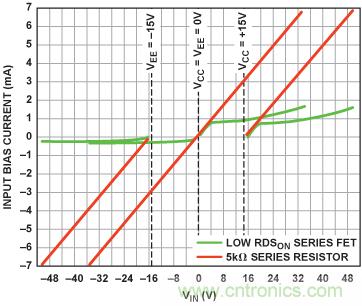

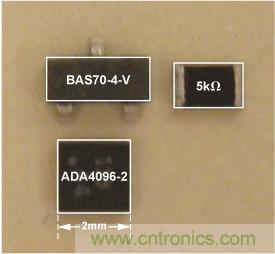

圖12顯示了2 mm × 2 mm LFCSP封裝的ADA4096-2和幾個(gè)常用于外部輸入保護(hù)的分立器件。ADA4096-2的集成保護(hù)使PCB尺寸大幅縮小���,其影響已包括在運(yùn)算放大器的技術(shù)規(guī)格中����。即使未施加電源���,它也能保護(hù)放大器(見(jiàn)圖13)��。此外����,ADA4091和ADA4096具有軌到軌輸入和輸出特性(RRIO),在整個(gè)過(guò)壓保護(hù)范圍內(nèi)都不會(huì)發(fā)生反相(見(jiàn)圖14)��。這些優(yōu)勢(shì)使得系統(tǒng)設(shè)計(jì)師可以少擔(dān)心電源時(shí)序控制和閂鎖問(wèn)題���。

圖12. 2 mm × 2 mm LFCSP封裝ADA4096-2占用的面積少于兩個(gè)常用于外部過(guò)壓保護(hù)的器件

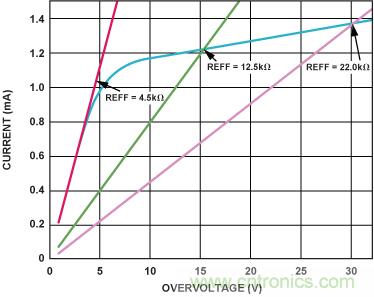

圖13. 有電源和無(wú)電源兩種情況下ADA4096-2輸入過(guò)壓保護(hù)的限流

圖14. ADA4096-2采用±10 V電源,輸入被拉至供電軌以上和以下30 V

結(jié)論

總而言之�,集成過(guò)壓保護(hù)具有許多優(yōu)勢(shì):

1.提高模擬信號(hào)鏈的魯棒性和精度

2.縮短產(chǎn)品上市時(shí)間(TTM)、設(shè)計(jì)時(shí)間����,降低測(cè)試要求

3.降低BOM(物料清單)成本

4.核準(zhǔn)器件清單所需的器件更少

5.PCB尺寸更小、密度更高

6.故障率更低

推薦閱讀:

(4)

(4)

(4)

(4)